Test Support

ARM DDI 0186A

Copyright © 2000 ARM Limited. All rights reserved.

10-3

10.2

Scan insertion and ATPG

This technique is covered in detail in the

ARM966E-S Implementation Guide

. Scan

insertion requires that all register elements are replaced by scannable versions that are

then connected up into a number of large scan chains. These scan chains are used to set

up data patterns on the combinatorial logic between the registers, and capture the logic

outputs. The logic outputs are then scanned out while the next data pattern is scanned in.

Automatic Test Pattern Generation

(ATPG) tools are used to create the necessary scan

patterns to test the logic, when the scan insertion has been performed. This technique

enables very high fault coverage to be achieved for the standard cell combinatorial

logic, typically in the 95-99% range.

Scan insertion does have an impact on the area and performance of the synthesized

design, due to the larger scan register elements and the serial routing between them.

However, to minimize these effects, the scan insertion is performed early in the

synthesis cycle and the design re-optimized with the scan elements in place.

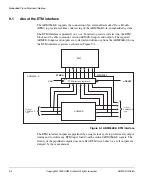

10.2.1

ARM966E-S INTEST wrapper

To facilitate testing of the shadow logic between the ARM966E-S scan chains and the

scan chains in an OEM ASIC, a synthesis option allows an INTEST wrapper to be

inserted into the ARM966E-S. The INTEST wrapper is a scan chain around the

boundary of the ARM966E-S, connecting to all input and output pins.

Note

•

Shadow logic is logic that is not ordinarily tested.

•

The INTEST wrapper is only required for embedded ARM966E-S.

•

The order of this scan chain is predetermined and must be maintained through

synthesis and place and route of the macrocell.

Summary of Contents for ARM966E-S

Page 6: ...Contents vi Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 20: ...Introduction 1 4 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 48: ...Tightly coupled SRAM 4 12 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 80: ...Bus Interface Unit 6 20 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 118: ...Debug Support 8 26 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 130: ...Test Support 10 8 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 142: ...Instruction cycle timings 11 12 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 158: ...Signal Descriptions A 16 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 176: ...AC Parameters B 18 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...