SRAM Stall Cycles

C-6

Copyright © 2000 ARM Limited. All rights reserved.

ARM DDI 0186A

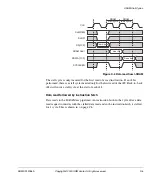

Figure C-5 Data read followed by instruction fetch

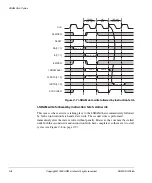

Simultaneous instruction fetch, data write

If the ARM9E-S performs a simultaneous data write and instruction fetch that both map

to I-SRAM address space, two stall cycles occur. The first cycle allows for the pipelined

write, the second cycle allows for the instruction fetch. The core cannot be enabled until

both accesses have completed (see Figure C-6 on page C-7).

CLK

DnMREQ

InMREQ

DnRW

DA[31:0]

IA[31:0]

I-SRAM

Addr

RDATA[31:0]

INSTR[31:0]

SYSCLKEN

Addr A(read)

Addr A

Addr B(fetch)

Addr B

Read data (A)

Read data (B)

stall

cycle

data

read

instr

fetch

Summary of Contents for ARM966E-S

Page 6: ...Contents vi Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 20: ...Introduction 1 4 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 48: ...Tightly coupled SRAM 4 12 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 80: ...Bus Interface Unit 6 20 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 118: ...Debug Support 8 26 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 130: ...Test Support 10 8 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 142: ...Instruction cycle timings 11 12 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 158: ...Signal Descriptions A 16 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 176: ...AC Parameters B 18 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...