Memory Map

3-2

Copyright © 2000 ARM Limited. All rights reserved.

ARM DDI 0186A

3.1

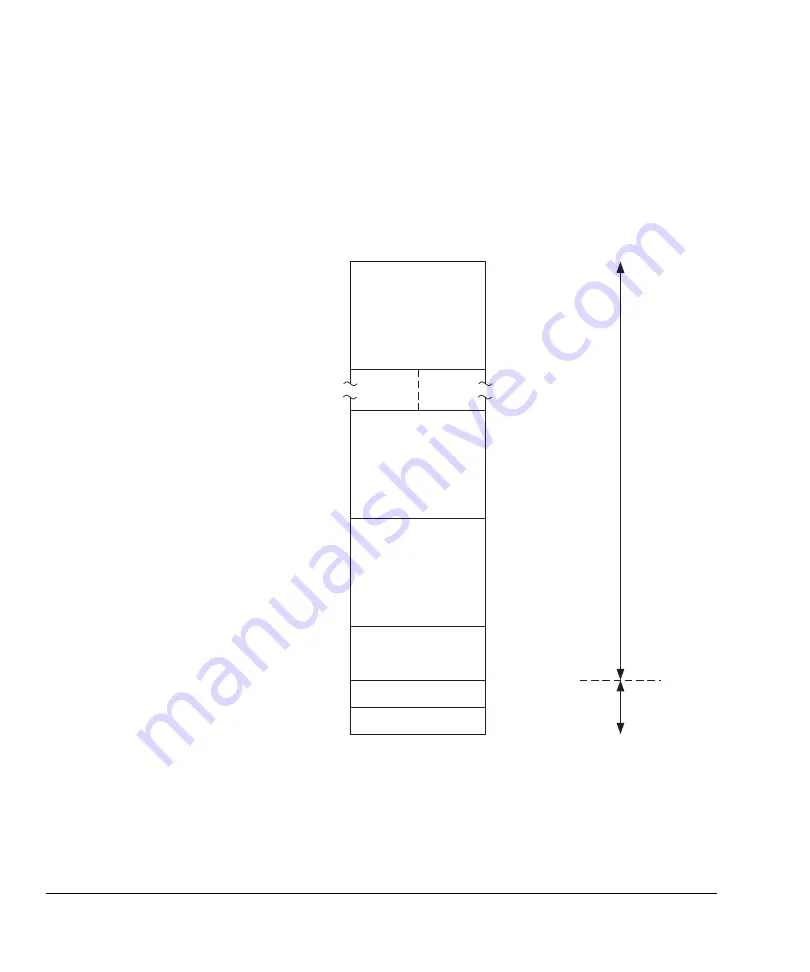

About the ARM966E-S memory map

The ARM966E-S couples Instruction and Data SRAM memories of configurable size

to the ARM9E-S core. This allows high-speed operation without incurring the

performance and power penalties of accessing the system bus. A write buffer is used to

minimize traffic on the AHB bus.

To provide simple control over the SRAM and write buffer, a fixed memory map is

implemented within the ARM966E-S. Figure 3-1 illustrates this map.

Figure 3-1 ARM966E-S memory map

256MB

256MB

256MB

128MB

64MB

64MB

AHB unbuffered

AHB buffered

AHB unbuffered

AHB buffered

D-SRAM

I-SRAM

Tightly-coupled

SRAM

AMBA AHB

0xFFFF FFFF

0xF000 0000

0x2FFF FFFF

0x2000 0000

0x1FFF FFFF

0x1000 0000

0x0FFF FFFF

0x0800 0000

0x07FF FFFF

0x0400 0000

0x03FF FFFF

0x0000 0000

Summary of Contents for ARM966E-S

Page 6: ...Contents vi Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 20: ...Introduction 1 4 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 48: ...Tightly coupled SRAM 4 12 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 80: ...Bus Interface Unit 6 20 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 118: ...Debug Support 8 26 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 130: ...Test Support 10 8 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 142: ...Instruction cycle timings 11 12 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 158: ...Signal Descriptions A 16 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 176: ...AC Parameters B 18 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...