Direct Memory Access (DMA)

5-4

Copyright © 2000 ARM Limited. All rights reserved.

ARM DDI 0186A

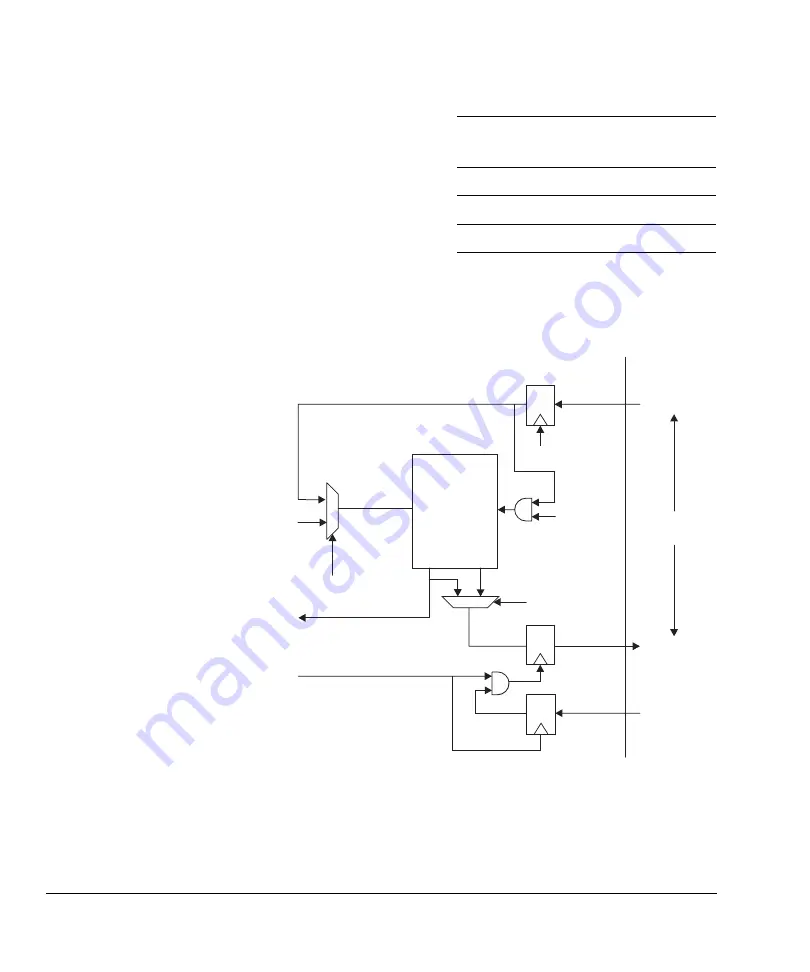

Figure 5-2 shows how the ARM966E-S DMA port interfaces to a dual-port RAM. For

modelling purposes, the dual-port DMA solution also supports the single-port access

route. Single-port access reduces performance in the dual-port solution and is unlikely

to be used, so to prevent the core from being stalled,

DMAWait

must be tied LOW.

Figure 5-2 Dual-port RAM DMA interface

Read

Write

Undefined

Write

Read

Undefined

Write

Write

Illegal

Table 5-1 Simultaneous access behavior (continued)

Core

access

DMA

access

behavior

CPU RAM Access

SP DMA Access

CPU Read Data

RAMRData1

CLK

DMACLK

SP DMA Access

RAMRData2

DP DMA Access

DMACLK

Dual Port

RAM

DMA Outputs

DMA

Port

DMA Inputs

ARM966E-S

Addr

WriteEnable

ChipSelect

DataIn

ByteWrite

Port1

Port2

Q1

Q2

0

1

1

0

DMAEnable

Summary of Contents for ARM966E-S

Page 6: ...Contents vi Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 20: ...Introduction 1 4 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 48: ...Tightly coupled SRAM 4 12 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 80: ...Bus Interface Unit 6 20 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 118: ...Debug Support 8 26 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 130: ...Test Support 10 8 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 142: ...Instruction cycle timings 11 12 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 158: ...Signal Descriptions A 16 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 176: ...AC Parameters B 18 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...