Direct Memory Access (DMA)

ARM DDI 0186A

Copyright © 2000 ARM Limited. All rights reserved.

5-5

5.2

Timing interface

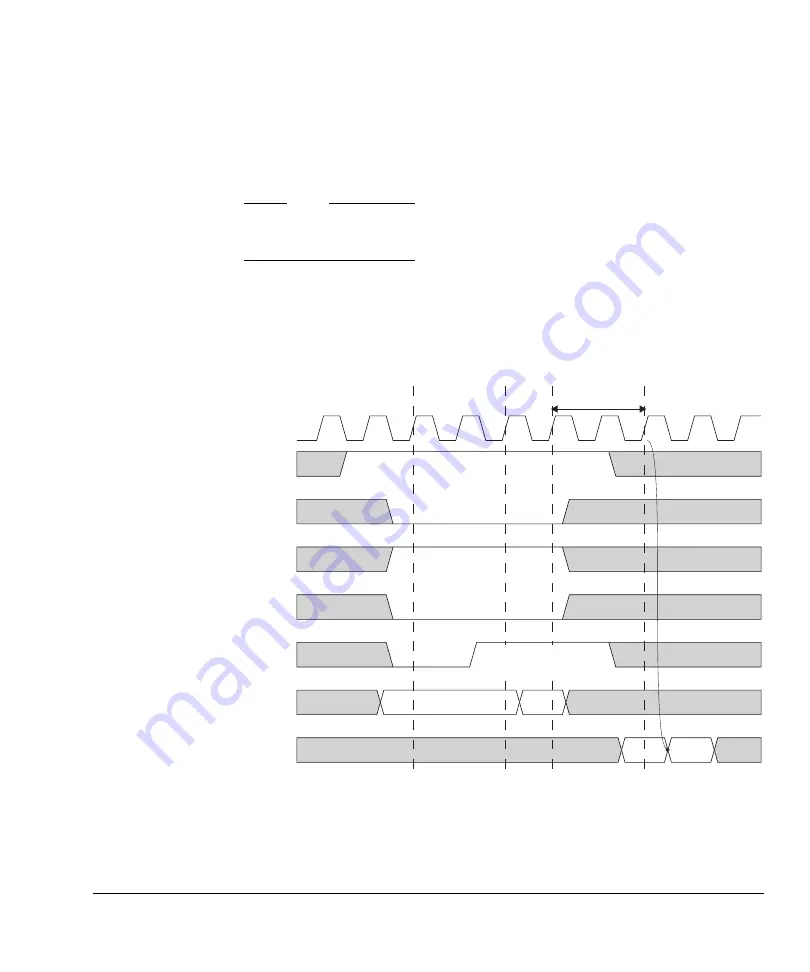

To ease the system integration task and to provide RAM independent timings, the

ARM966E-S registers all DMA inputs and outputs. This section details the behavior of

the ARM966E-S for DMA read and writes to single and dual-port RAMs.

Note

The dual-port RAM DMA solution also supports the single-port operation and so the

single-port diagrams are also applicable to dual-port RAMs.

5.2.1

Single-port RAM reads

Figure 5-3 shows DMA read operation from a single-port RAM.

Figure 5-3 Single-port RAM DMA reads

CLK

DMAENABLE

DMAnREQ

DMAWait

DMAnRW

DMAReady

DMAAddr

DMARData

DMA read request

Read latency

Core Stalled

A1

A2

D1

D2

Summary of Contents for ARM966E-S

Page 6: ...Contents vi Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 20: ...Introduction 1 4 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 48: ...Tightly coupled SRAM 4 12 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 80: ...Bus Interface Unit 6 20 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 118: ...Debug Support 8 26 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 130: ...Test Support 10 8 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 142: ...Instruction cycle timings 11 12 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 158: ...Signal Descriptions A 16 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 176: ...AC Parameters B 18 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...