A10.3

Attributes of the CHI master interface

The table lists the possible values for the read and write issuing capabilities if the processor includes four

cores.

n

Number of cores.

m

1 if the processor is configured for the ACP interface, 0 if it is not.

w

(write issuing capa1.

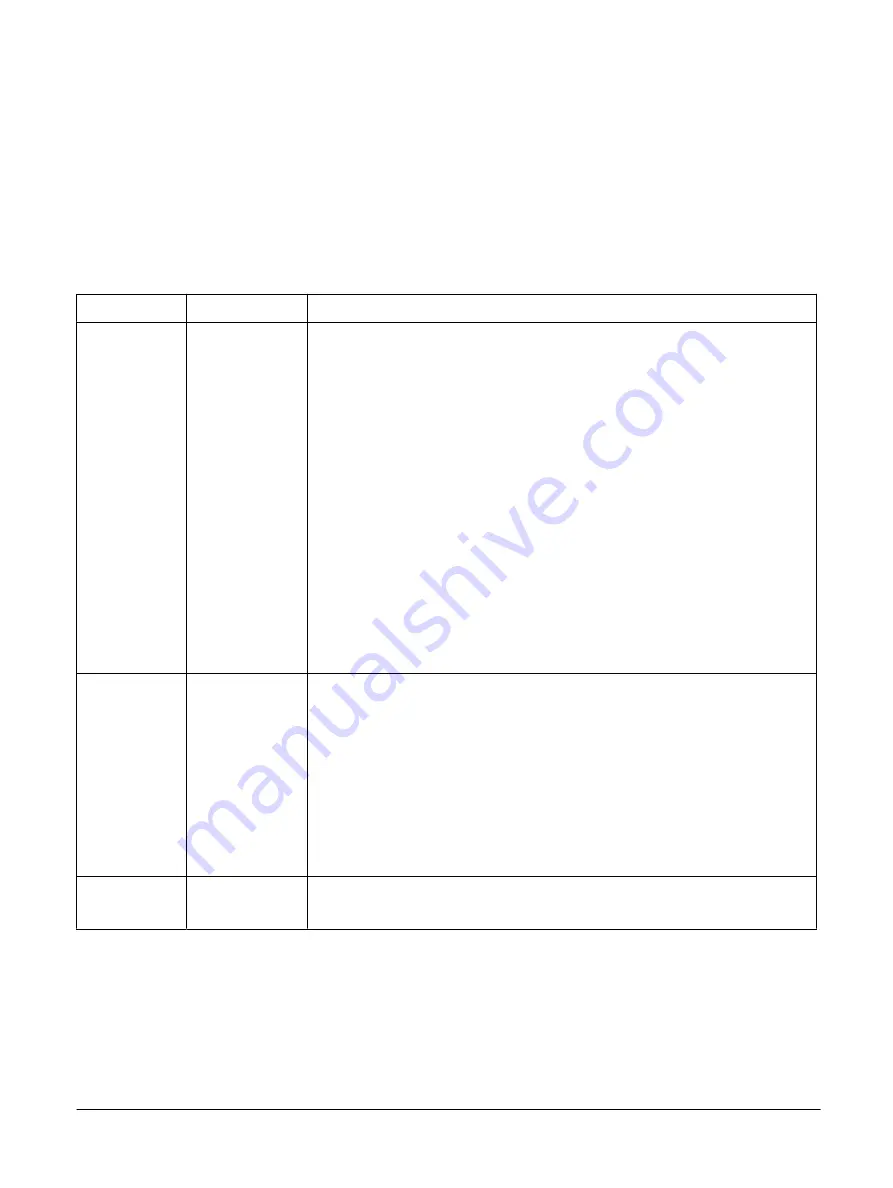

Table A10-3 Attributes of the CHI master memory interface

Attribute

Value

Comments

Write issuing

capability

Configuration

dependent

The maximum number of writes varies, depending on the configuration of the processor:

•

The number of cores.

•

The presence of the L2 cache.

If no L2 cache is configured:

One

core

5 outstanding writes.

2-4

cores

8 outstanding writes.

If an L2 cache is configured:

One

core

7 outstanding writes.

2-4

cores

10 outstanding write.

A cluster with four cores, with L2 cache, can issue 10 outstanding transactions. A processor

with one core, without L2 cache, can issue five outstanding transactions.

All outstanding transactions use a unique ID.

Read issuing

capability

8n + 4m + 1

8 for each core in the cluster including up to:

•

8 data linefills.

•

4 Non-cacheable or Device data reads.

•

1 Non-cacheable TLB page-walk read.

•

3 instruction linefills.

•

5 coherency operations.

•

1 barrier operation.

•

8 DVM messages.

If an ACP is configured, up to 4 ACP linefill requests can be generated. 1 barrier operation

is generated from the cluster.

Exclusive thread

capability

n

Each core can have 1 exclusive access sequence in progress.

A10 CHI Master Interface

A10.3 Attributes of the CHI master interface

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

A10-128

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......