A10.5

CHI transactions

CHI transactions are sent to a specific node in the interconnect based on the following criteria:

• Type of access.

• Address of the access.

• Settings of the System Address Map.

Addresses that map to an HN-F node can be marked as cacheable memory in the page tables, and can

take part in the cache coherency protocol. Addresses that map to an HN-I or MN must be marked as

device or non-cacheable memory.

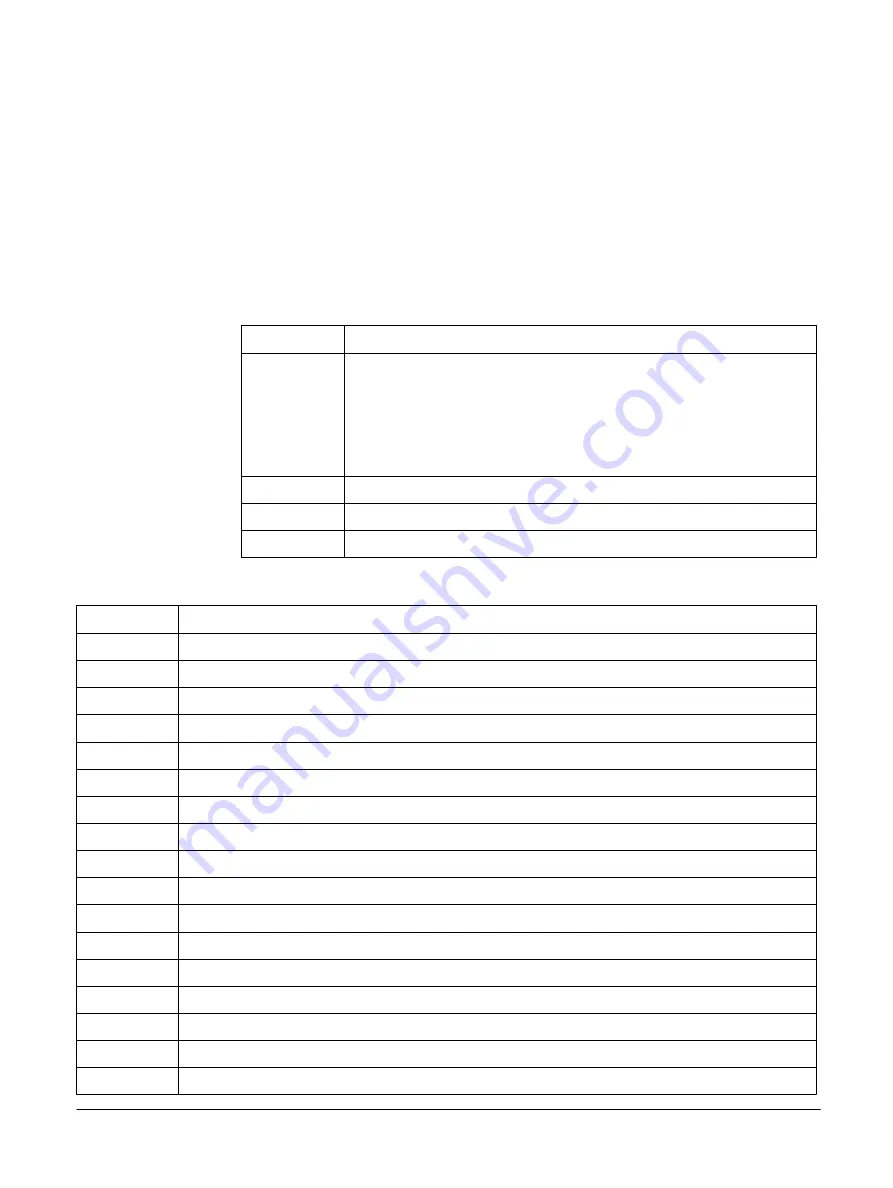

Table A10-5 CHI transaction IDs

Transaction ID Description

000nnxxx

Transaction from core nn. Can be a:

•

Read transaction.

•

Write transaction.

•

Cache maintenance transaction.

•

DVM transaction.

•

Barrier transaction.

001001xx

Transaction from the ACP interface. Can be a read or write.

00101110

Barrier generated in response to a DVM sync snoop from the interconnect.

0100xxxx

Eviction from L1 or L2 cache. The number of IDs used depends on the configuration.

Table A10-6 CHI transactions

Transaction

Operation

ReadNoSnp

Non-cacheable loads or instruction fetches. Linefills of non-shareable cache lines into L1 or L2.

ReadOnce

Cacheable loads that are not allocating into the cache, or cacheable instruction fetches when there is no L2 cache.

ReadClean

Not used.

ReadShared

L1 Data linefills started by a load instruction, or L2 linefills started by an instruction fetch.

ReadUnique

L1 Data linefills started by a store instruction.

CleanUnique

Store instructions that hit in the cache but the line is not in a unique coherence state.

MakeUnique

Store instructions of a full cache line of data, that miss in the caches, and are allocating into the L2 cache.

CleanShared

Cache maintenance instructions.

CleanInvalid

Cache maintenance instructions.

MakeInvalid

Cache maintenance instructions.

DVMOp

TLB and instruction cache maintenance instructions.

EOBarrier

DMB instructions.

ECBarrier

DSB instructions. DVM sync snoops received from the interconnect.

WriteNoSnpPtl

Non-cacheable store instructions.

WriteNoSnpFull Non-cacheable store instructions, or evictions of non-shareable cache lines from the L1 and L2 cache.

WriteUniqueFull Cacheable writes of a full cache line, that are not allocating into L1 or L2 caches, for example streaming writes.

WriteUniquePtl

Cacheable writes of less than a full cache line that are not allocating into L1 or L2.

A10 CHI Master Interface

A10.5 CHI transactions

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

A10-131

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......