B1.18

c15 registers

The processor can access different 32-bit wide system registers. Registers where CRn has the value

fifteen are called c15 registers.

The following table shows the 32-bit wide system registers you can access when the processor is in

AArch32 state and the value of CRn is c15.

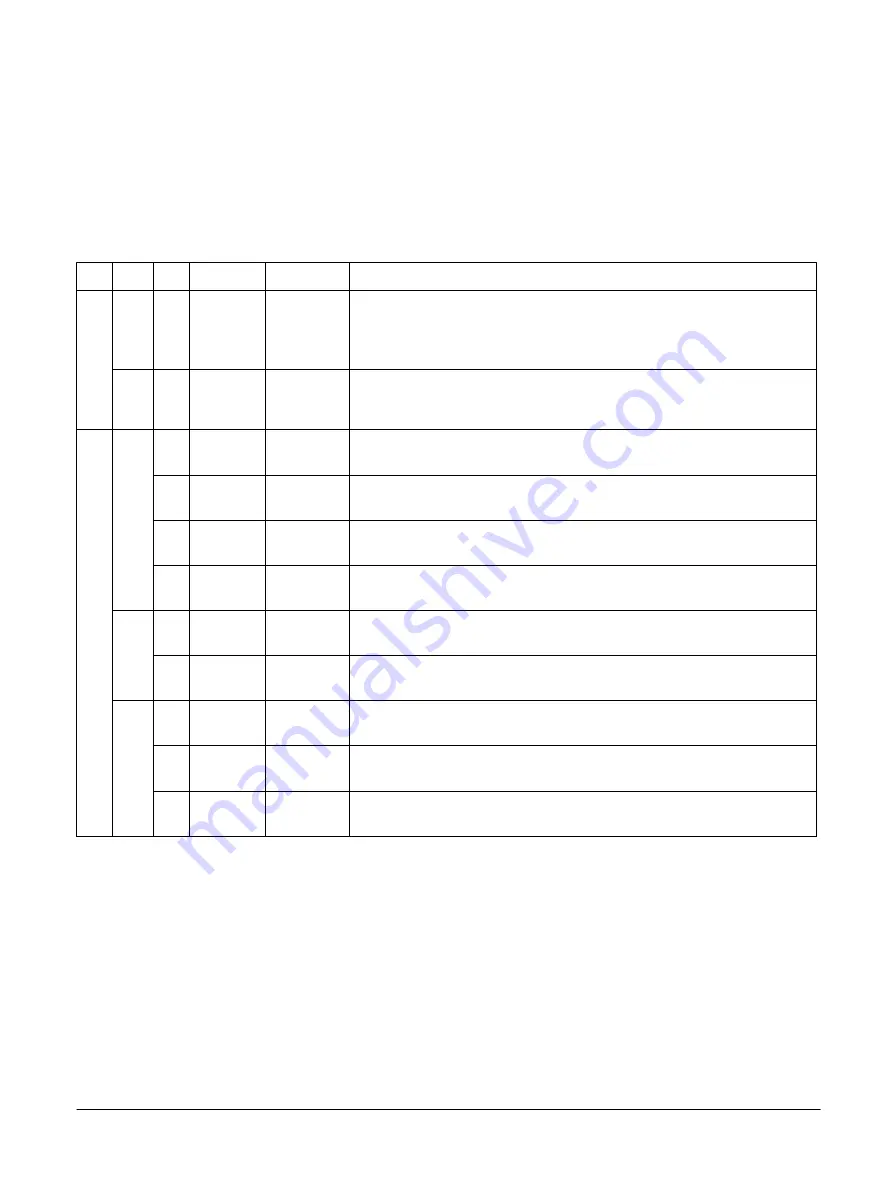

Table B1-17 c15 register summary

Op1 CRm Op2 Name

Reset

Description

1

c0

0

L2ACTLR

0x80000000

B1.91 L2 Auxiliary Control Register

This is the reset value for an ACE interface. For an AXI interface the reset value is

0x80000008

. For a CHI interface the reset value is

0x80004008

.

c3

0

CBAR

-

B1.38 Configuration Base Address Register

The reset value depends on the processor configuration.

3

c0

0

CDBGDR0 UNK

Cache Debug Data Register 0, see

C5.1 About direct access to internal memory

1

CDBGDR1 UNK

Cache Debug Data Register 1, see

C5.1 About direct access to internal memory

2

CDBGDR2 UNK

Cache Debug Data Register 2, see

C5.1 About direct access to internal memory

3

CDBGDR3 UNK

Cache Debug Data Register 3, see

C5.1 About direct access to internal memory

c2

0

CDBGDCT UNK

Cache Debug Data Cache Tag Read Operation Register, see

1

CDBGICT

UNK

Cache Debug Instruction Cache Tag Read Operation Register, see

c4

0

CDBGDCD UNK

Cache Debug Cache Debug Data Cache Data Read Operation Register, see

C5.1 About direct access to internal memory

1

CDBGICD

UNK

Cache Debug Instruction Cache Data Read Operation Register, see

direct access to internal memory

2

CDBGTD

UNK

Cache Debug TLB Data Read Operation Register, see

B1 AArch32 system registers

B1.18 c15 registers

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

B1-174

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......