B1.27

AArch32 Secure registers

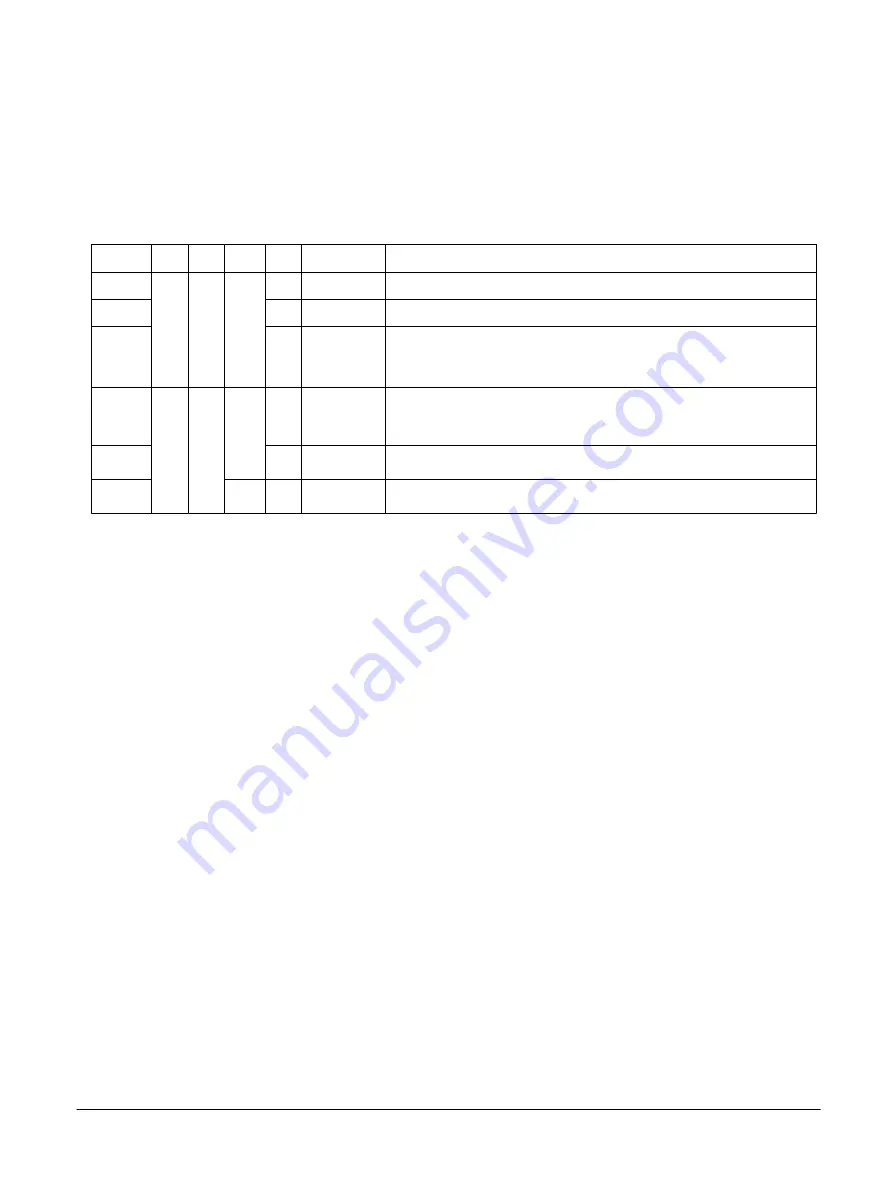

The following table shows the Secure registers.

See the

Arm

®

Architecture Reference Manual Armv8, for Armv8-A architecture profile

for more

information.

Table B1-26 Security registers

Name

CRn Op1 CRm Op2 Reset

Description

SCR

c1

0

c1

0

0x00000000

B1.104 Secure Configuration Register

SDER

1

UNK

Secure Debug Enable Register

NSACR

2

0x00000000

B1.98 Non-Secure Access Control Register

If EL3 is AArch64, then the NSACR reads as

0x00000C00

.

VBAR

c12

0

c0

0

0x00000000

B1.119 Vector Base Address Register

0x00000000

is the secure reset value and UNK is the non-secure reset value.

MVBAR

1

UNK

Monitor Vector Base Address Register

ISR

c1

0

UNK

Interrupt Status Register

B1 AArch32 system registers

B1.27 AArch32 Secure registers

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

B1-185

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......