0b01

Normal memory, Outer Write-Back Write-Allocate Cacheable.

0b10

Normal memory, Outer Write-Through Cacheable.

0b11

Normal memory, Outer Write-Back no Write-Allocate Cacheable.

IRGN0, [9:8]

Inner cacheability attribute for memory associated with translation table walks using TTBR0.

The possible values are:

0b00

Normal memory, Inner Non-cacheable.

0b01

Normal memory, Inner Write-Back Write-Allocate Cacheable.

0b10

Normal memory, Inner Write-Through Cacheable.

0b11

Normal memory, Inner Write-Back no Write-Allocate Cacheable.

[7:3]

Reserved,

RES0

.

T0SZ, [2:0]

Size offset of the memory region addressed by TTBR0. The region size is 2

(32-TSIZE)

bytes.

The processor does not use the implementation-defined bit, HTCR[30], so this bit is

RES0

.

To access the HTCR:

MRC p15, 4, <Rt>, c2, c0, 2; Read HTCR into Rt

MCR p15, 4, <Rt>, c2, c0, 2; Write Rt to HTCR

Register access is encoded as follows:

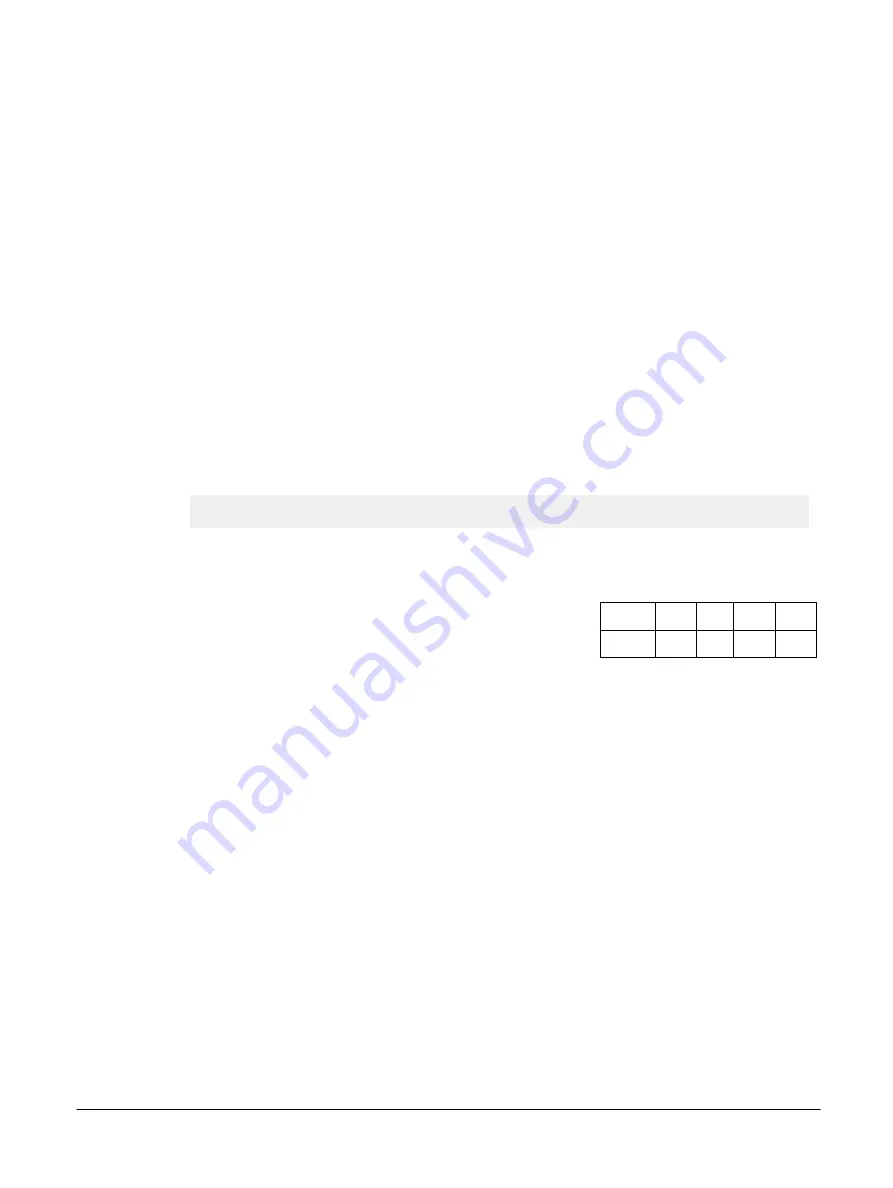

Table B1-54 HTCR access encoding

coproc opc1 CRn CRm opc2

1111

100

0010 0000 010

B1 AArch32 system registers

B1.70 Hyp Translation Control Register

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

B1-264

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......