B2.13

AArch64 Virtualization registers

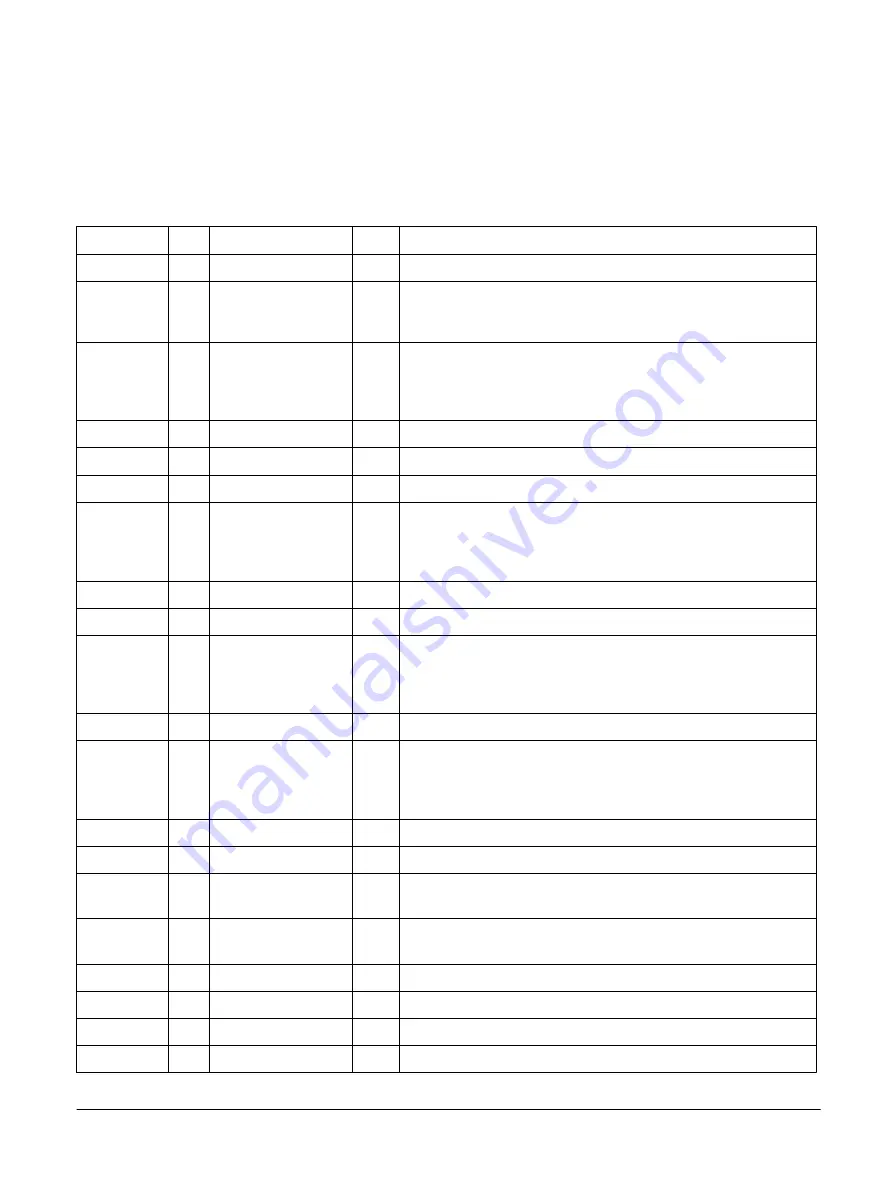

The following table shows the virtualization registers in AArch64 state.

Bits[63:32] are reset to

0x00000000

for all 64-bit registers in this table.

Table B2-13 AArch64 virtualization registers

Name

Type Reset

Width Description

VPIDR_EL2

RW

0x411FD040

32

B2.104 Virtualization Processor ID Register, EL2

VMPIDR_EL2 RW

-

64

B2.103 Virtualization Multiprocessor ID Register, EL2

The reset value is the value of the Multiprocessor Affinity Register.

SCTLR_EL2

RW

0x30C50838

32

B2.91 System Control Register, EL2

The reset value depends on inputs,

CFGTE

and

CFGEND

. The value

shown assumes these signals are set to LOW.

ACTLR_EL2

RW

0x00000000

32

B2.20 Auxiliary Control Register, EL2

HCR_EL2

RW

0x0000000000000002

64

B2.48 Hypervisor Configuration Register, EL2

MDCR_EL2

RW

0x00000006

32

B2.80 Monitor Debug Configuration Register, EL2

CPTR_EL2

RW

0x000033FF

32

B2.32 Architectural Feature Trap Register, EL2

The reset value is

0x0000BFFF

if Advanced SIMD and floating-point are

not implemented.

HSTR_EL2

RW

0x00000000

32

B2.50 Hyp System Trap Register, EL2

HACR_EL2

RW

0x00000000

32

B2.47 Hyp Auxiliary Configuration Register, EL2

TTBR0_EL2

RW

UNK

64

Translation Table Base Address Register 0, EL3

See the

Arm

®

Architecture Reference Manual Armv8, for Armv8-A

architecture profile

for more information.

TCR_EL2

RW

UNK

32

B2.95 Translation Control Register, EL2

VTTBR_EL2

RW

UNK

64

Virtualization Translation Table Base Address Register, EL2

See the

Arm

®

Architecture Reference Manual Armv8, for Armv8-A

architecture profile

.

VTCR_EL2

RW

UNK

32

B2.105 Virtualization Translation Control Register, EL2

DACR32_EL2 RW

UNK

32

B2.39 Domain Access Control Register, EL2

AFSR0_EL2

RW

0x00000000

32

B2.22 Auxiliary Fault Status Register 0, EL1, EL2, and EL3

AFSR1_EL2

RW

0x00000000

32

B2.23 Auxiliary Fault Status Register 1, EL1, EL2, and EL3

ESR_EL2

RW

UNK

32

B2.42 Exception Syndrome Register, EL2

FAR_EL2

RW

UNK

64

B2.45 Fault Address Register, EL2

HPFAR_EL2

RW

UNK

64

B2.49 Hypervisor IPA Fault Address Register, EL2

MAIR_EL2

RW

UNK

64

B2.78 Memory Attribute Indirection Register, EL2

B2 AArch64 system registers

B2.13 AArch64 Virtualization registers

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

B2-377

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......