1

The register is write accessible from Non-secure EL1.

Write access from Non-secure EL1 also requires ACTLR_EL3[4] to be set.

[3:2]

Reserved,

RES0

.

CPUECTLR_EL1 access control, [1]

CPUECTLR_EL1 write access control. The possible values are:

0

The register is not write accessible from Non-secure EL1.This is the reset value.

1

The register is write accessible from Non-secure EL1.

Write access from Non-secure EL1 also requires ACTLR_EL3[1] to be set.

CPUACTLR_EL1 access control, [0]

CPUACTLR_EL1 write access control. The possible values are:

0

The register is not write accessible from Non-secure EL1.This is the reset value.

1

The register is write accessible from Non-secure EL1.

Write access from Non-secure EL1 also requires ACTLR_EL3[0] to be set.

To access the ACTLR_EL2:

MRS <Xt>, ACTLR_EL2 ; Read ACTLR_EL2 into Xt

MSR ACTLR_EL2, <Xt> ; Write Xt to ACTLR_EL2

Register access is encoded as follows:

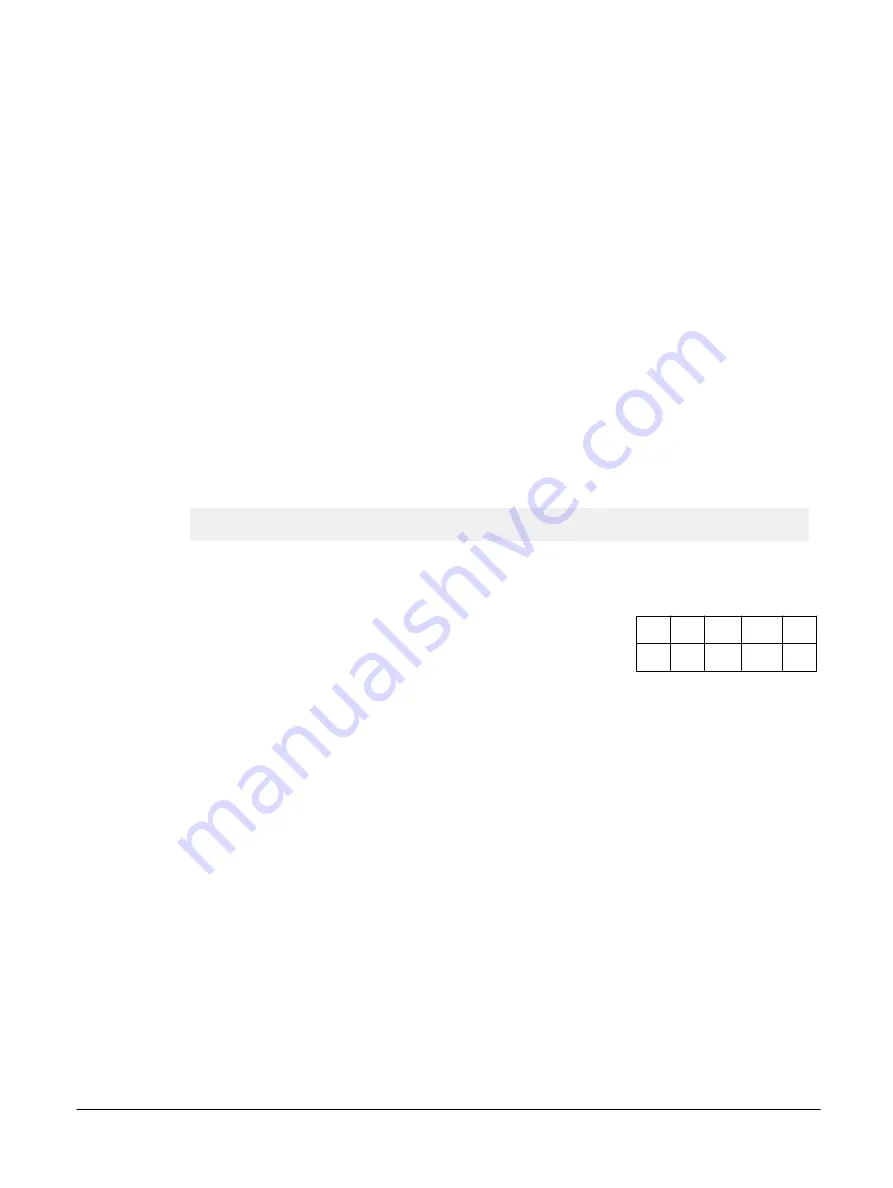

Table B2-18 ACTLR_EL2 access encoding

op0 op1 CRn CRm op2

11

100 0001 0000 001

B2 AArch64 system registers

B2.20 Auxiliary Control Register, EL2

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

B2-388

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......