B2.44

Fault Address Register, EL1

The FAR_EL1 characteristics are:

Purpose

Holds the faulting Virtual Address for all synchronous instruction or data aborts, or exceptions

from a misaligned PC or a Watchpoint debug event, taken to EL1.

Usage constraints

This register is accessible as follows:

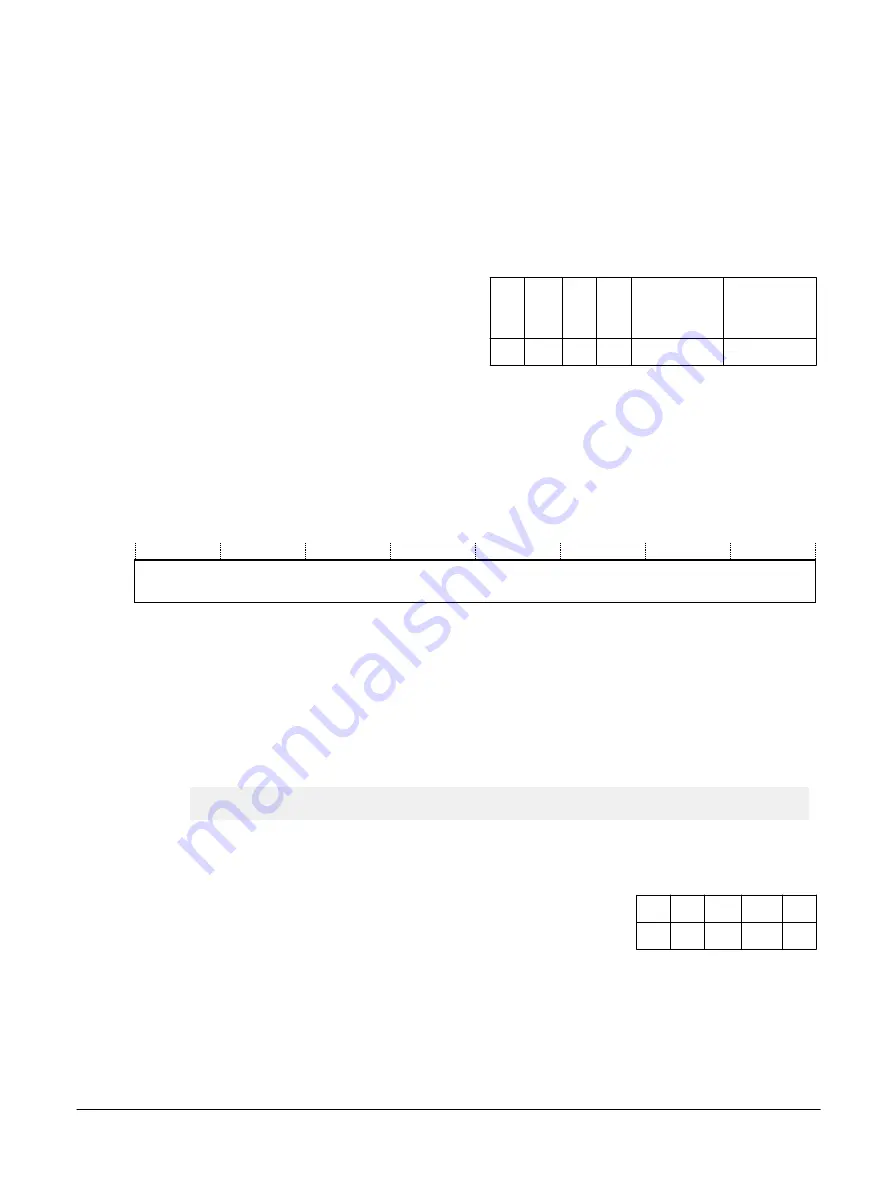

EL0 EL1

(NS)

EL1

(S)

EL2 EL3

(SCR.NS = 1)

EL3

(SCR.NS = 0)

-

RW

RW RW RW

RW

Configurations

FAR_EL1[31:0] is architecturally mapped to AArch32 register DFAR (NS). See

FAR_EL1[63:32] is architecturally mapped to AArch32 register IFAR (NS). See

B1.86 Instruction Fault Address Register

.

Attributes

FAR_EL1 is a 64-bit register.

VA

63

0

Figure B2-19 FAR_EL1 bit assignments

VA, [63:0]

The faulting Virtual Address for all synchronous instruction or data aborts, or an exception from

a misaligned PC, taken in EL1.

If a memory fault that sets the FAR is generated from one of the data cache instructions, this

field holds the address specified in the register argument of the instruction.

To access the FAR_EL1:

MRS <Xt>, FAR_EL1 ; Read EL1 Fault Address Register

MSR FAR_EL1, <Xt> ; Write EL1 Fault Address Register

Register access is encoded as follows:

Table B2-38 FAR_EL1 access encoding

op0 op1 CRn CRm op2

11

000 0110 0000 000

B2 AArch64 system registers

B2.44 Fault Address Register, EL1

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

B2-429

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......