0

Event counting prohibited in Secure state. This is the reset value.

1

Event counting allowed in Secure state.

SDD, [16]

AArch64 secure debug disable. Disables Software debug exceptions from Secure state if Secure

EL1 is using AArch64, other than from Software breakpoint instructions. The possible values

are:

0

Debug exceptions from Secure EL0 are enabled, and debug exceptions from Secure EL1 are

enabled if MDSCR_EL1.KDE is 1 and PSTATE.D is 0.

1

Debug exceptions from all exception levels in Secure state are disabled.

The reset value is

UNKNOWN

.

SPD32, [15:14]

AArch32 secure privileged debug. Enables or disables debug exceptions from Secure state if

Secure EL1 is using AArch32, other than Software breakpoint instructions. The possible values

are:

0b00

Legacy mode. Debug exceptions from Secure EL1 are enabled only if

AArch32SelfHostedSecurePrivilegedInvasiveDebugEnabled()

.

0b01

Reserved.

0b10

Secure privileged debug disabled. Debug exceptions from Secure EL1 are disabled.

0b11

Secure privileged debug enabled. Debug exceptions from Secure EL1 are enabled.

The reset value is

UNKNOWN

.

[13:11]

Reserved,

RES0

.

TDOSA, [10]

Trap accesses to the OS debug system registers, OSLAR_EL1, OSLSR_EL1, OSDLR_EL1, and

DBGPRCR_EL1 OS.

0

Accesses are not trapped.

1

Accesses to the OS debug system registers are trapped to EL3.

The reset value is

UNKNOWN

.

TDA, [9]

Trap accesses to the remaining sets of debug registers to EL3.

0

Accesses are not trapped.

1

Accesses to the remaining debug system registers are trapped to EL3.

The reset value is

UNKNOWN

.

[8:7]

Reserved,

RES0

.

TPM, [6]

Trap Performance Monitors accesses. The possible values are:

0

Accesses are not trapped.

1

Accesses to the Performance Monitor registers are trapped to EL3.

The reset value is

UNKNOWN

.

B2 AArch64 system registers

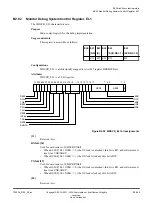

B2.81 Monitor Debug Configuration Register, EL3

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

B2-504

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......