B2.88

Reset Vector Base Address Register, EL3

The RVBAR_EL3 characteristics are:

Purpose

Contains the address that execution starts from after reset when executing in the AArch64 state.

RVBAR_EL3 is part of the Reset management registers functional group.

Usage constraints

This register is accessible as follows:

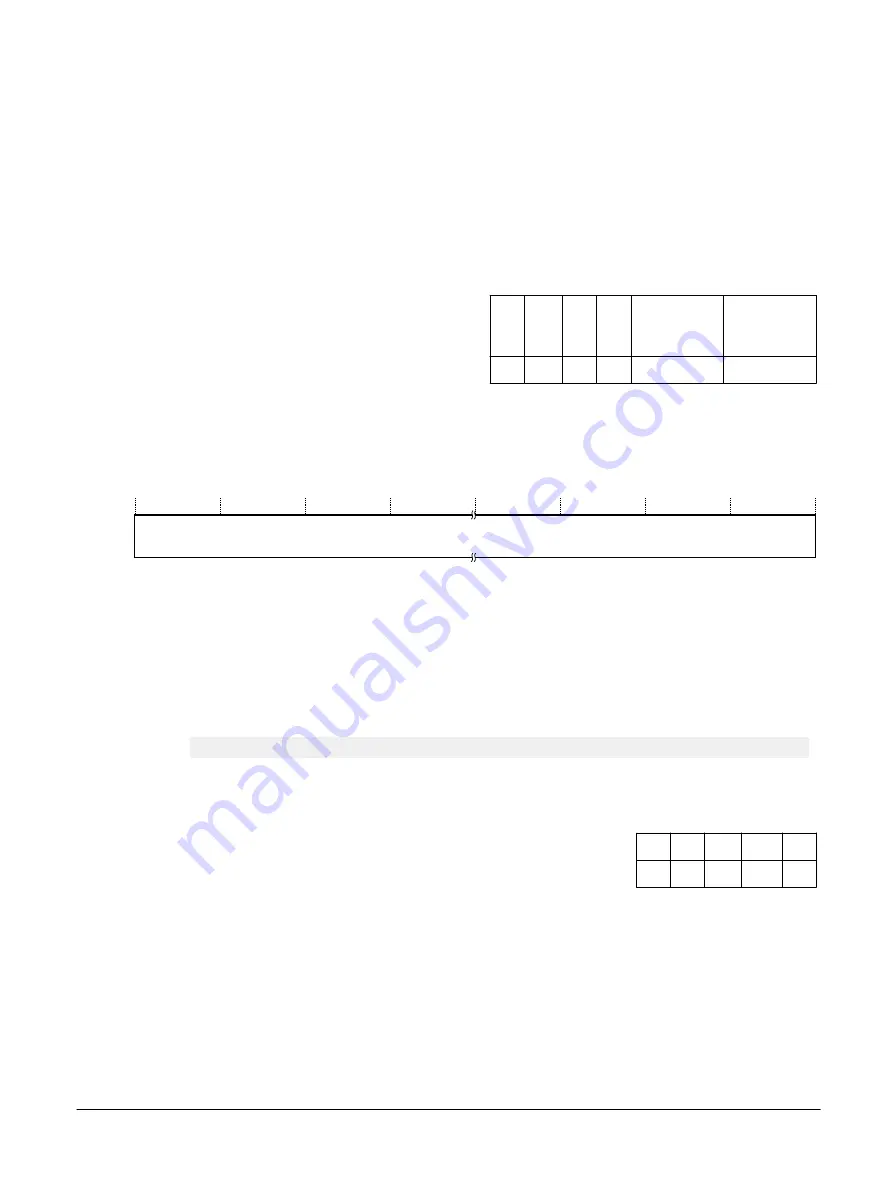

EL0 EL1

(NS)

EL1

(S)

EL2 EL3

(SCR.NS = 1)

EL3

(SCR.NS = 0)

-

-

-

-

RO

RO

Configurations

There is no configuration information.

Attributes

RVBAR_EL3 is a 64-bit register.

0

Reset Vector Base Address

63

Figure B2-59 RVBAR_EL3 bit assignments

RVBA, [63:0]

Reset Vector Base Address. The address that execution starts from after reset when executing in

64-bit state. Bits[1:0] of this register are

0b00

, as this address must be aligned, and bits [63:40]

are

0x000000

because the address must be within the physical address size supported by the

processor.

To access the RVBAR_EL3:

MRS <Xt>, RVBAR_EL3 ; Read RVBAR_EL3 into Xt

Register access is encoded as follows:

Table B2-82 RVBAR_EL3 access encoding

op0 op1 CRn CRm op2

11

110 1100 0000 001

B2 AArch64 system registers

B2.88 Reset Vector Base Address Register, EL3

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

B2-521

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......