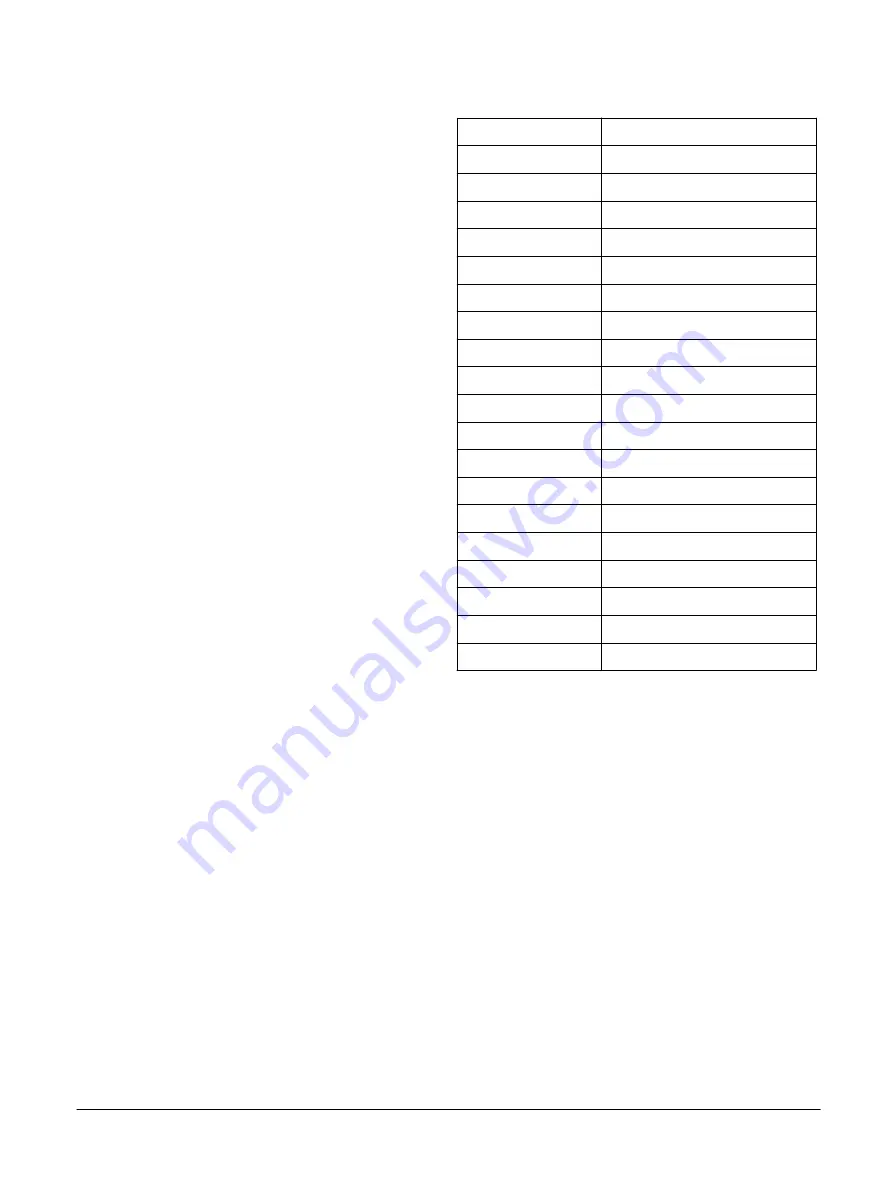

Table C1-4 Address mapping for APB components in a v7 Debug memory map

Address offset [21:0] Mapped to

0x00000

-

0x00FFF

APB ROM table for the processor

0x01000

-

0x07FFF

Reserved for other debug components

0x08000

-

0x0FFFF

Reserved for future expansion

0x10000

-

0x10FFF

Core 0 Debug

0x11000

-

0x11FFF

Core 0 PMU

0x12000

-

0x12FFF

Core 1 Debug

0x13000

-

0x13FFF

Core 1 PMU

0x14000

-

0x14FFF

Core 2 Debug

0x15000

-

0x15FFF

Core 2 PMU

0x16000

-

0x16FFF

Core 3 Debug

0x17000

-

0x17FFF

Core 3 PMU

0x18000

-

0x18FFF

Core 0 CTI

0x19000

-

0x19FFF

Core 1 CTI

0x1A000

-

0x1AFFF

Core 2 CTI

0x1B000

-

0x1BFFF

Core 3 CTI

0x1C000

-

0x1CFFF

Core 0 Trace

0x1D000

-

0x1DFFF

Core 1 Trace

0x1E000

-

0x1EFFF

Core 2 Trace

0x1F000

-

0x1FFFF

Core 3 Trace

C1 Debug

C1.6 Debug memory map

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

C1-582

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......