C2.3

Performance monitoring events

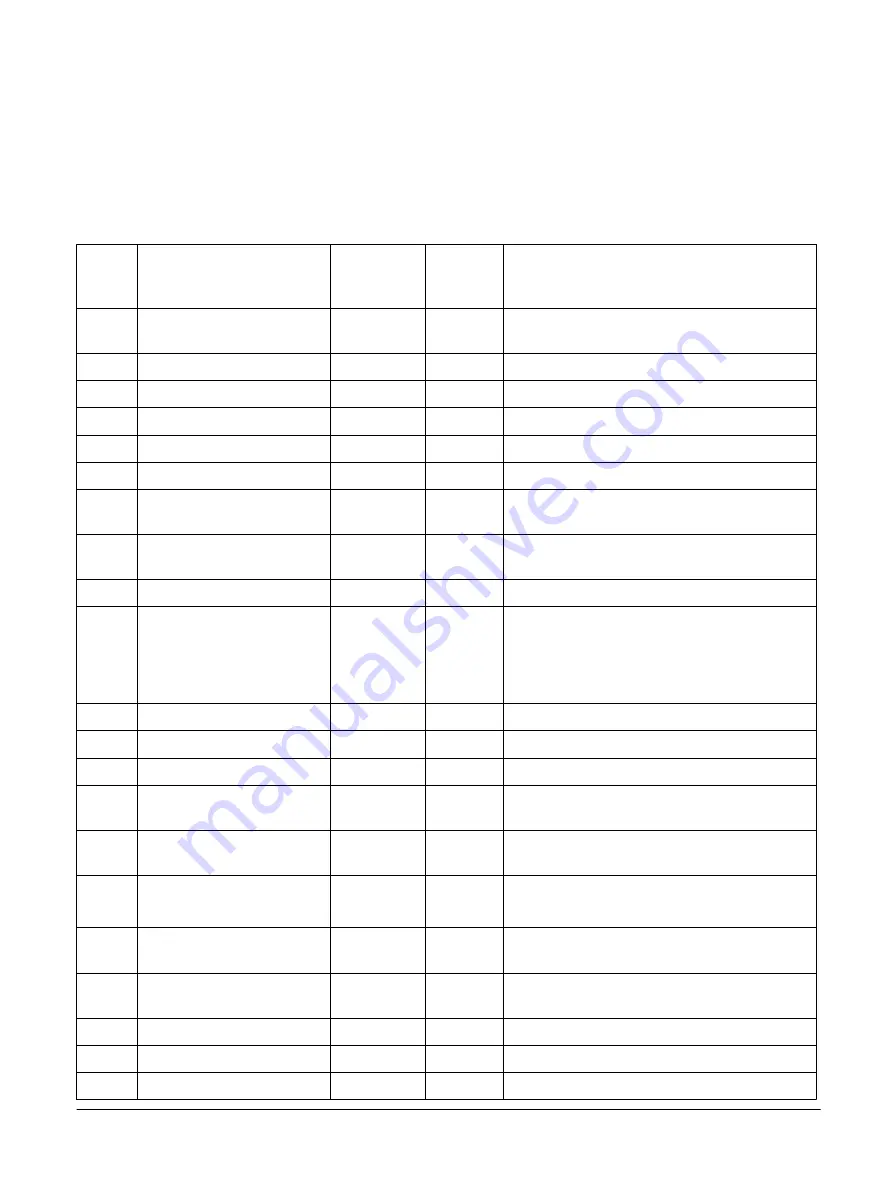

The PMU monitors events in the processor and uses reference numbers for significant ones.

The following table shows the bit position of each event on the event bus. Event reference numbers that

are not listed are reserved.

Table C2-3 Performance monitoring events

Number Event mnemonic

PMU event

bus to

external

PMU

event bus

to trace

Event name

0x00

SW_INCR

-

-

Software increment. The register is incremented only

on writes to the Software Increment Register.

0x01

L1I_CACHE_REFILL

[0]

[0]

L1 Instruction cache refill.

0x02

L1I_TLB_REFILL

[1]

[1]

L1 Instruction TLB refill.

0x03

L1D_CACHE_REFILL

[2]

[2]

L1 Data cache refill.

0x04

L1D_CACHE

[3]

[3]

L1 Data cache access.

0x05

L1D_TLB_REFILL

[4]

[4]

L1 Data TLB refill.

0x06

LD_RETIRED

[5]

[5]

Instruction that is architecturally executed, condition

check pass - load.

0x07

ST_RETIRED

[6]

[6]

Instruction that is architecturally executed, condition

check pass - store.

0x08

INST_RETIRED

[7]

[7]

Instruction that is architecturally executed.

-

-

[8]

[8]

Two instructions are architecturally executed.

Counts every cycle in which two instructions are

architecturally retired. Event

0x08

, INST_RETIRED,

always counts when this event counts.

0x09

EXC_TAKEN

[9]

[9]

Exception taken.

0x0A

EXC_RETURN

[10]

[10]

Exception return.

0x0B

CID_WRITE_RETIRED

[11]

[11]

Change to Context ID retired.

0x0C

PC_WRITE_RETIRED

[12]

[12]

Instruction that is architecturally executed, condition

check pass, software change of the PC.

0x0D

BR_IMMED_RETIRED

[13]

[13]

Instruction that is architecturally executed, immediate

branch.

0x0E

BR_RETURN_RETIRED

-

-

Instruction that is architecturally executed, condition

code check pass, procedure return.

0x0F

UNALIGNED_LDST_RETIRED [14]

[14]

Instruction that is architecturally executed, condition

check pass, unaligned load or store.

0x10

BR_MIS_PRED

[15]

[15]

Mispredicted or not predicted branch that is

speculatively executed.

0x11

CPU_CYCLES

-

-

Cycle.

0x12

BR_PRED

[16]

[16]

Predictable branch that is speculatively executed.

0x13

MEM_ACCESS

[17]

[17]

Data memory access.

C2 PMU

C2.3 Performance monitoring events

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

C2-588

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......