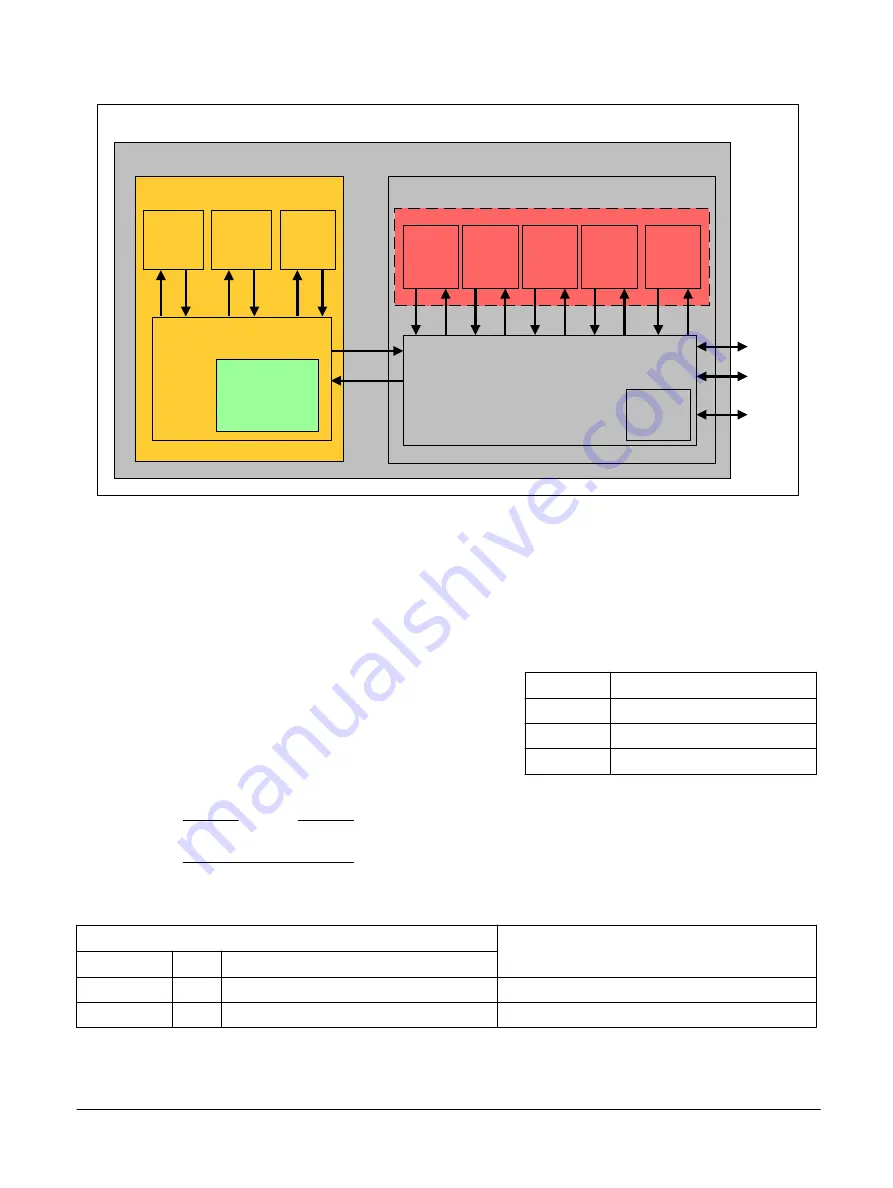

System

PDSOC

Processor

PDMERCURY

L2

PDL2*

Core <n>

PDCPU<n>

Core <n>

excluding RAM

APB

Master

Interface

Data

cache

RAM

ATB

Instruction

cache

RAM

TLB RAM

*If implementation includes Dormant mode support

Advanced SIMD

and floating-point

L2 excluding RAM

L1

Duplicate

tag RAM

0

L1

Duplicate

tag RAM

1

L1

Duplicate

tag RAM

2

L1

Duplicate

tag RAM

3

L2 cache

RAM

PDADVSIMD<n>

Debug

domain

registers

Figure A4-1 Power domains

The power domains can be controlled independently to give different combinations of powered-up and

powered-down domains. However, only some powered-up and powered-down domain combinations are

valid and supported.

Table A4-2 Power state description

Power state Description

Off

Block is power gated

Ret

Logic or RAM retention power only

On

Block is active

The following tables show the supported power domain states for the processor.

Caution

States that are not shown in the tables are unsupported and must not occur.

Table A4-3 Supported processor power states

Power domains

Description

PDMERCURY PDL2 PDCPU<n>

Off

Off

Off

Processor off.

Off

On/Ret Off

L2 cache dormant mode.

A4 Power Management

A4.1 Power domains

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

A4-59

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......