C6.1

AArch32 debug register summary

This section summarizes the 32-bit and 64-bit debug control registers that are accessible in the AArch32

Execution state from the internal CP14 interface.

These registers, listed in the following table, are accessed by the

MCR

and

MRC

instructions in the order of

CRn, op2, CRm, Op1 or

MCRR

and

MRRC

instructions in the order of CRm, Op1. For those registers not

described in this chapter, see the

Arm

®

Architecture Reference Manual Armv8, for Armv8-A architecture

profile

.

C8.1 Memory-mapped debug register summary

for a complete list of registers

accessible from the external debug interface.

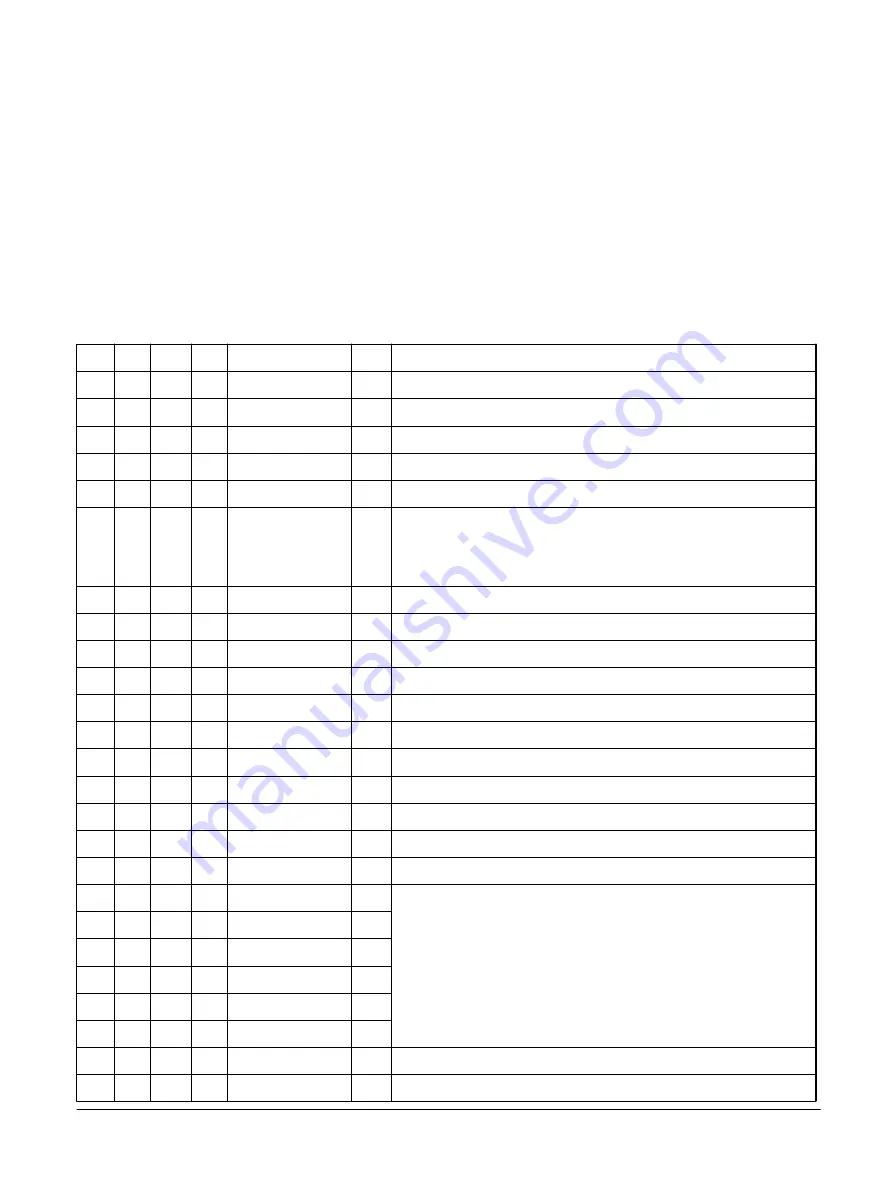

Table C6-1 AArch32 debug register summary

CRn Op2 CRm Op1 Name

Type Description

c0

0

c0

0

DBGDIDR

RO

c0

0

c1

0

DBGDSCRint

RO

Debug Status and Control Register, Internal View

c0

0

c2

0

DBGDCCINT

RW

Debug Comms Channel Interrupt Enable Register

c0

0

c5

0

DBGDTRTXint

WO

Debug Data Transfer Register, Transmit, Internal View

DBGDTRRXint

RO

Debug Data Transfer Register, Receive, Internal View

c0

0

c6

0

DBGWFAR

RW

Watchpoint Fault Address Register,

RES0

Previously returned information about the address of the instruction that

accessed a watchpoint address. This register is now deprecated and is

RES0

.

c0

0

c7

0

DBGVCR

RW

Debug Vector Catch Register

c0

2

c0

0

DBGDTRRXext

RW

Debug Data Transfer Register, Receive, External View

c0

2

c2

0

DBGDSCRext

RW

Debug Status and Control Register, External View

c0

2

c3

0

DBGDTRTXext

RW

Debug Data Transfer Register, Transmit, External View

c0

2

c6

0

DBGOSECCR

RW

Debug OS Lock Exception Catch Control Register

c0

4

c0

0

DBGBVR0

RW

Debug Breakpoint Value Register 0

c0

4

c1

0

DBGBVR1

RW

Debug Breakpoint Value Register 1

c0

4

c2

0

DBGBVR2

RW

Debug Breakpoint Value Register 2

c0

4

c3

0

DBGBVR3

RW

Debug Breakpoint Value Register 3

c0

4

c4

0

DBGBVR4

RW

Debug Breakpoint Value Register 4

c0

4

c5

0

DBGBVR5

RW

Debug Breakpoint Value Register 5

c0

5

c0

0

DBGBCR0

RW

C6.2 Debug Breakpoint Control Registers

c0

5

c1

0

DBGBCR1

RW

c0

5

c2

0

DBGBCR2

RW

c0

5

c3

0

DBGBCR3

RW

c0

5

c4

0

DBGBCR4

RW

c0

5

c5

0

DBGBCR5

RW

c0

6

c0

0

DBGWVR0

RW

Debug Watchpoint Value Register 0

c0

6

c1

0

DBGWVR1

RW

Debug Watchpoint Value Register 1

C6 AArch32 debug registers

C6.1 AArch32 debug register summary

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

C6-620

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......