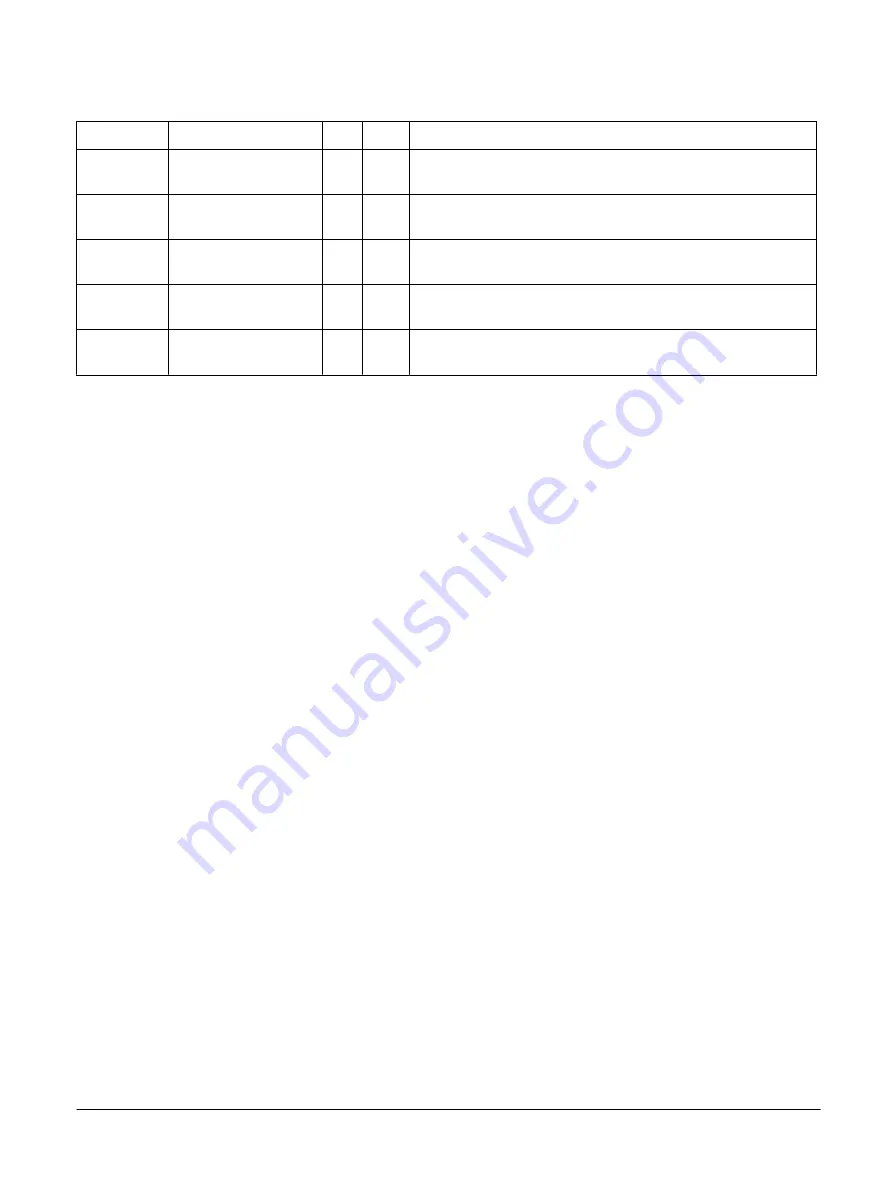

Table C8-1 Memory-mapped debug register summary (continued)

Offset

Name

Type Width Description

0xFEC

EDPIDR3

RO

32

C8.12 External Debug Peripheral Identification Register 3

0xFF0

EDCIDR0

RO

32

C8.16 External Debug Component Identification Register 0

0xFF4

EDCIDR1

RO

32

C8.17 External Debug Component Identification Register 1

0xFF8

EDCIDR2

RO

32

C8.18 External Debug Component Identification Register 2

0xFFC

EDCIDR3

RO

32

C8.19 External Debug Component Identification Register 3

C8 Memory-mapped debug registers

C8.1 Memory-mapped debug register summary

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

C8-647

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......