C9.5

ROM Table Peripheral Identification Registers

The ROM Table Peripheral Identification Registers provide standard information required for all

components that conform to the Arm Debug Interface Architecture Specification, ADIv5.0 to ADIv5.2.

There are eight registers listed in register number order in the following table.

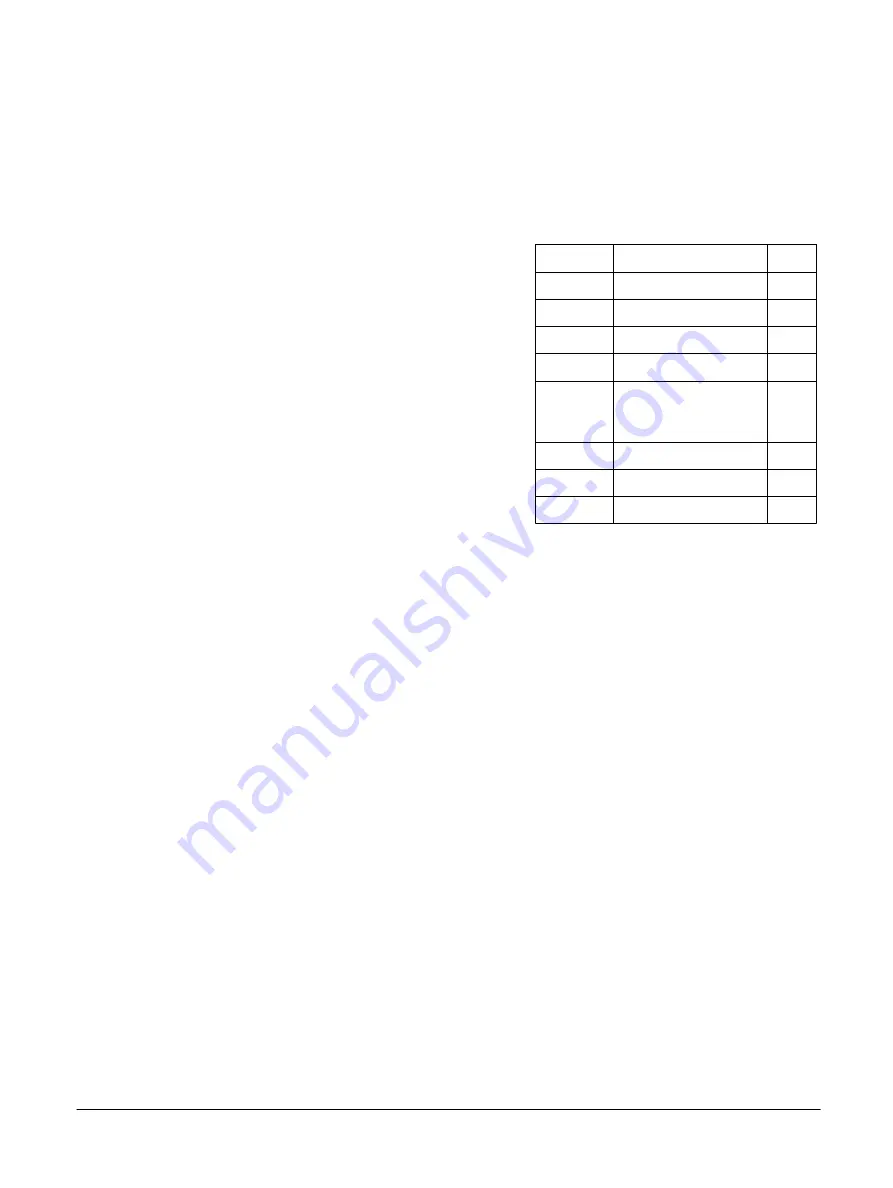

Table C9-4 Summary of the ROM Table Peripheral Identification Registers

Register

Value

Offset

ROMPIDR4

0x04

0xFD0

ROMPIDR5

0x00

0xFD4

ROMPIDR6

0x00

0xFD8

ROMPIDR7

0x00

0xFDC

ROMPIDR0

0xAA

for v8 memory map.

0xE0

for v7 memory map.

0xFE0

ROMPIDR1

0xB4

0xFE4

ROMPIDR2

0x3B

0xFE8

ROMPIDR3

0x00

0xFEC

Only bits[7:0] of each Peripheral ID Register are used, with bits[31:8] reserved. Together, the eight

Peripheral ID Registers define a single 64-bit Peripheral ID.

C9 ROM table

C9.5 ROM Table Peripheral Identification Registers

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

C9-677

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......