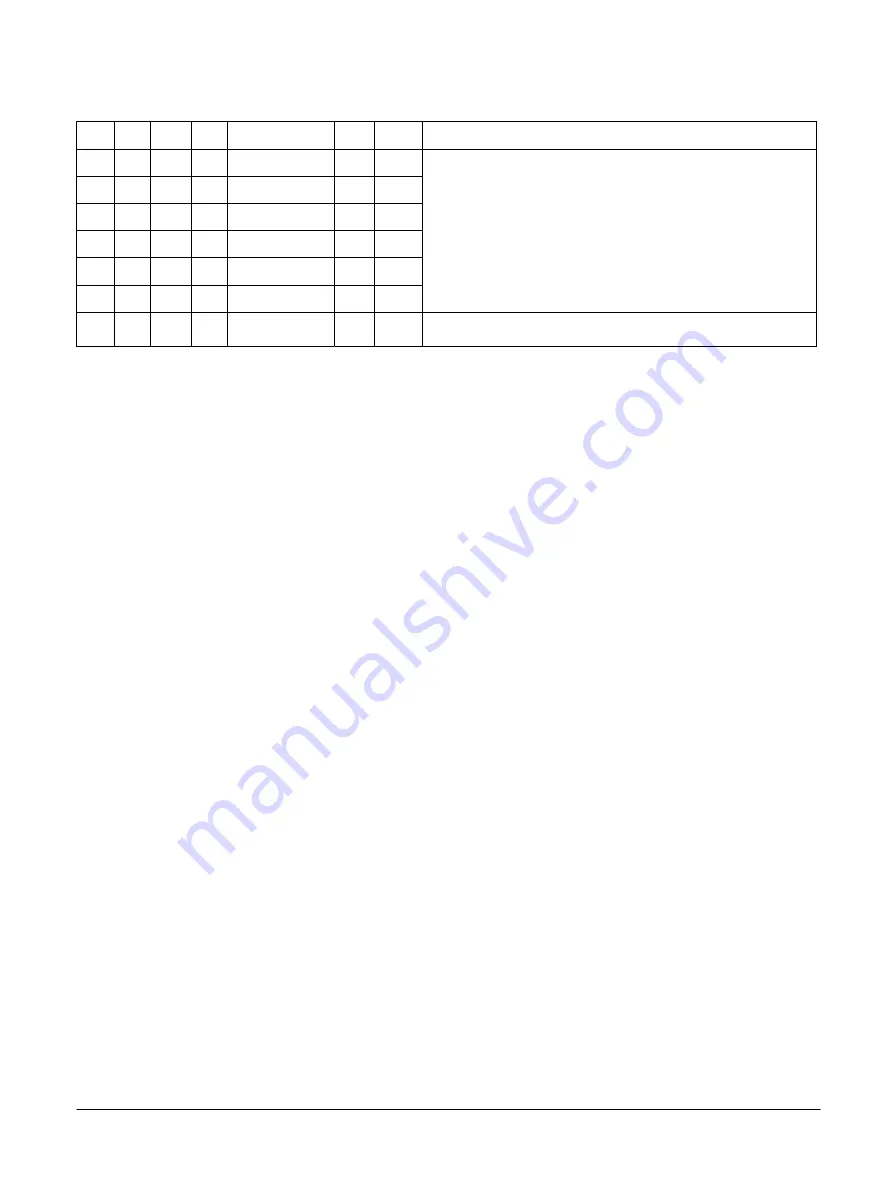

Table C10-1 PMU register summary in the AArch32 Execution state (continued)

CRn Op1 CRm Op2 Name

Type Width Description

c14

0

c12

0

PMEVTYPER0

RW

32

Performance Monitors Event Type Registers

c14

0

c12

1

PMEVTYPER1

RW

32

c14

0

c12

2

PMEVTYPER2

RW

32

c14

0

c12

3

PMEVTYPER3

RW

32

c14

0

c12

4

PMEVTYPER4

RW

32

c14

0

c12

5

PMEVTYPER5

RW

32

c14

0

c15

7

PMCCFILTR

RW

32

Performance Monitors Cycle Count Filter Register

C10 PMU registers

C10.1 AArch32 PMU register summary

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

C10-691

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......