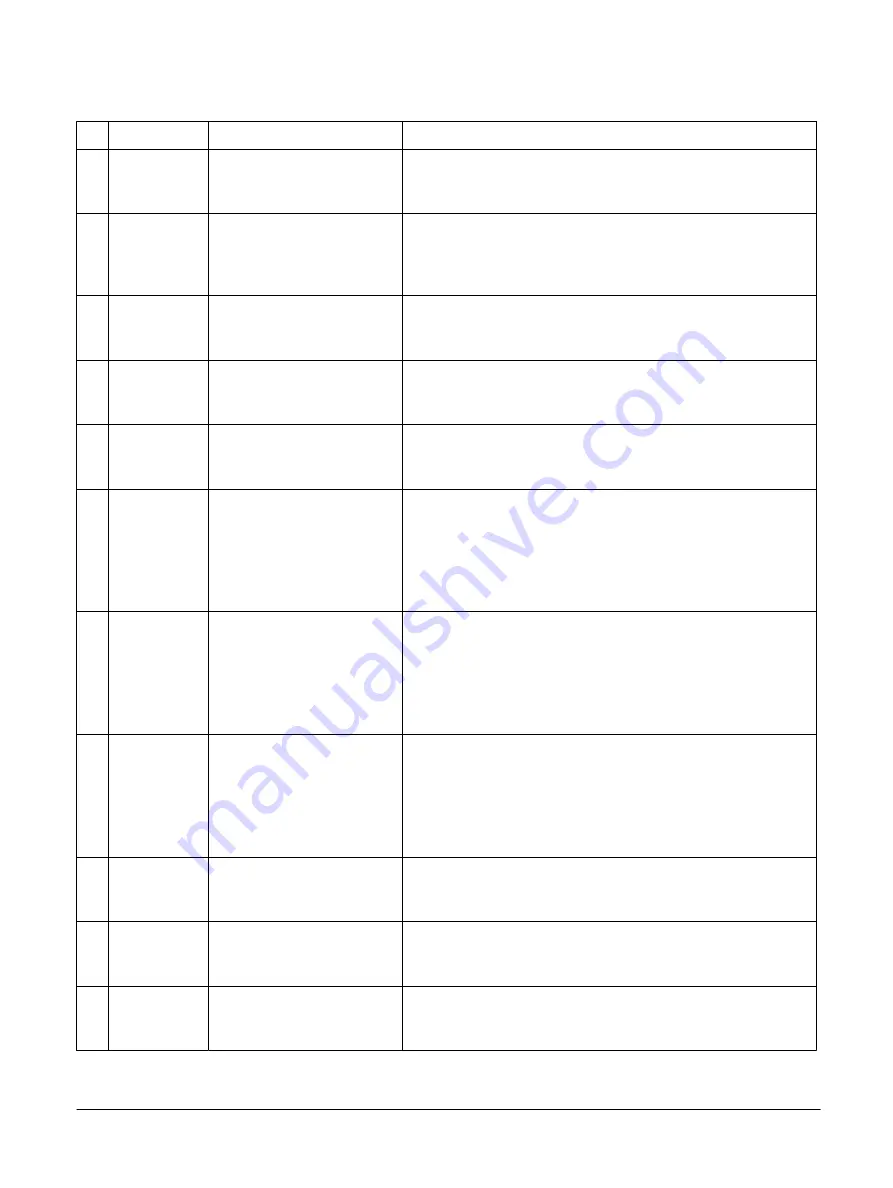

Table C10-2 PMU events (continued)

Bit Event number Event mnemonic

Description

[29]

0x1D

BUS_CYCLES

Bus cycle:

1

This event is implemented.

[28]

0x1C

TTBR_WRITE_RETIRED

TTBR write, architecturally executed, condition check pass - write to

translation table base:

0

This event is not implemented.

[27]

0x1B

INST_SPEC

Instruction speculatively executed:

1

This event is implemented.

[26]

0x1A

MEMORY_ERROR

Local memory error:

1

This event is implemented.

[25]

0x19

BUS_ACCESS

Bus access:

1

This event is implemented.

[24]

0x18

L2D_CACHE_WB

L2 Data cache Write-Back:

0

This event is not implemented if the Cortex

‑

A35 processor has

been configured without an L2 cache.

1

This event is implemented if the Cortex

‑

A35 processor has been

configured with an L2 cache.

[23]

0x17

L2D_CACHE_REFILL

L2 Data cache refill:

0

This event is not implemented if the Cortex

‑

A35 processor has

been configured without an L2 cache.

1

This event is implemented if the Cortex

‑

A35 processor has been

configured with an L2 cache.

[22]

0x16

L2D_CACHE

L2 Data cache access:

0

This event is not implemented if the Cortex

‑

A35 processor has

been configured without an L2 cache.

1

This event is implemented if the Cortex

‑

A35 processor has been

configured with an L2 cache.

[21]

0x15

L1D_CACHE_WB

L1 Data cache Write-Back:

1

This event is implemented.

[20]

0x14

L1I_CACHE

L1 Instruction cache access:

1

This event is implemented.

[19]

0x13

MEM_ACCESS

Data memory access:

1

This event is implemented.

C10 PMU registers

C10.3 Performance Monitors Common Event Identification Register 0

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

C10-696

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......