C10.5

AArch64 PMU register summary

The PMU counters and their associated control registers are accessible in the AArch64 Execution state

with

MRS

and

MSR

instructions.

The following table gives a summary of the Cortex

‑

A35 PMU registers in the AArch64 Execution state.

For those registers not described in this chapter, see the

Arm

®

Architecture Reference Manual Armv8, for

Armv8-A architecture profile

.

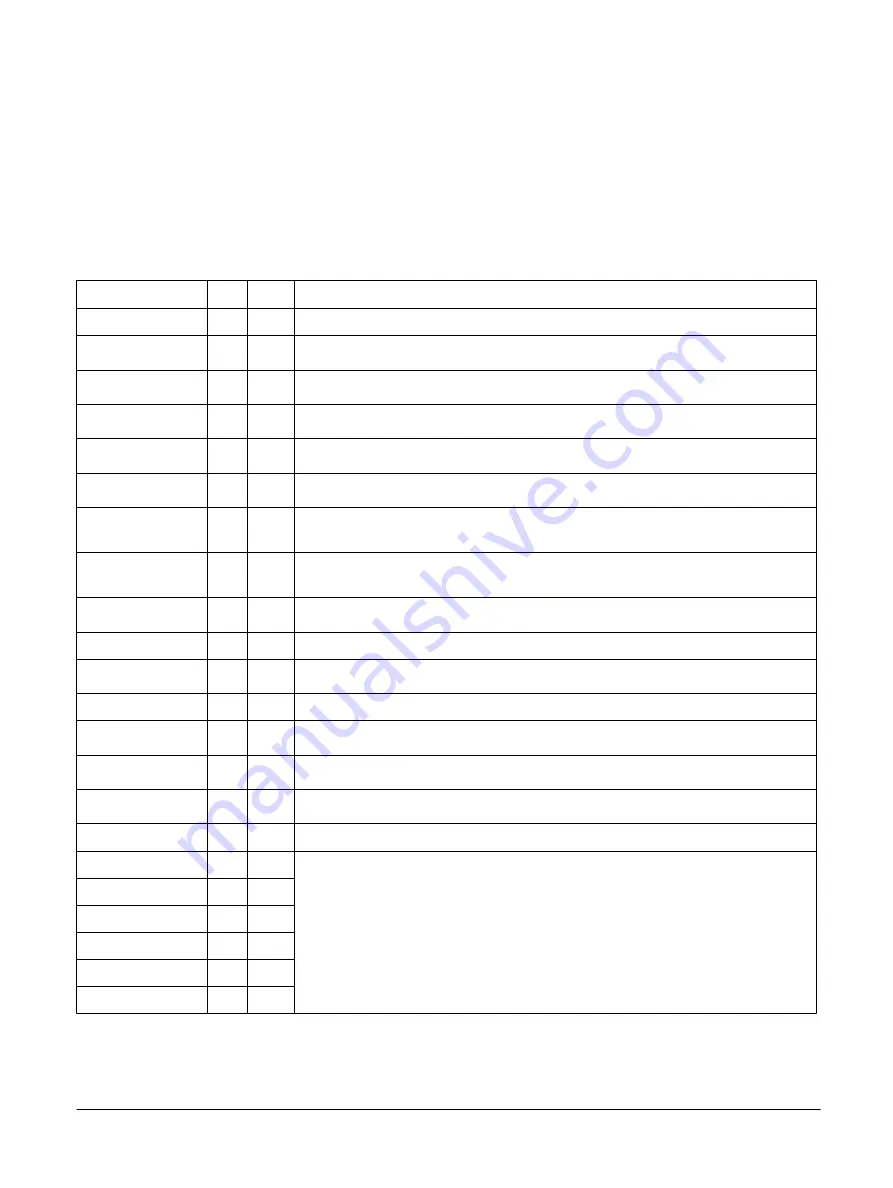

Table C10-4 PMU register summary in the AArch64 Execution state

Name

Type Width Description

PMCR_EL0

RW

32

C10.6 Performance Monitors Control Register, EL0

PMCNTENSET_EL0 RW

32

Performance Monitors Count Enable Set Register

PMCNTENCLR_EL0 RW

32

Performance Monitors Count Enable Clear Register

PMOVSCLR_EL0

RW

32

Performance Monitors Overflow Flag Status Register

PMSWINC_EL0

WO

32

Performance Monitors Software Increment Register

PMSELR_EL0

RW

32

Performance Monitors Event Counter Selection Register

PMCEID0_EL0

RO

32

C10.7 Performance Monitors Common Event Identification Register 0, EL0

PMCEID1_EL0

RO

32

C10.8 Performance Monitors Common Event Identification Register 1, EL0

PMCCNTR_EL0

RW

64

Performance Monitors Cycle Count Register

PMXEVTYPER_EL0 RW

32

Performance Monitors Selected Event Type and Filter Register

PMCCFILTR_EL0

RW

32

Performance Monitors Cycle Count Filter Register

PMXEVCNTR0_EL0 RW

32

Performance Monitors Selected Event Count Register

PMUSERENR_EL0

RW

32

Performance Monitors User Enable Register

PMINTENSET_EL1

RW

32

Performance Monitors Interrupt Enable Set Register

PMINTENCLR_EL1 RW

32

Performance Monitors Interrupt Enable Clear Register

PMOVSSET_EL0

RW

32

Performance Monitors Overflow Flag Status Set Register

PMEVCNTR0_EL0

RW

32

Performance Monitors Event Count Registers

PMEVCNTR1_EL0

RW

32

PMEVCNTR2_EL0

RW

32

PMEVCNTR3_EL0

RW

32

PMEVCNTR4_EL0

RW

32

PMEVCNTR5_EL0

RW

32

C10 PMU registers

C10.5 AArch64 PMU register summary

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

C10-702

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......