C10.6

Performance Monitors Control Register, EL0

The PMCR_EL0 characteristics are:

Purpose

Provides details of the Performance Monitors implementation, including the number of counters

implemented, and configures and controls the counters.

Usage constraints

This register is accessible as follows:

EL0 EL1

(NS)

EL1

(S)

EL2 EL3

(SCR.NS = 1)

EL3

(SCR.NS = 0)

RW RW

RW RW RW

RW

This register is accessible at EL0 when PMUSERENR_EL0.EN is set to 1.

Configurations

PMCR_EL0 is architecturally mapped to the AArch32 PMCR register. See

.

PMCR[6:0] is architecturally mapped to external PMCR_EL0 register.

Attributes

PMCR_EL0 is a 32-bit register.

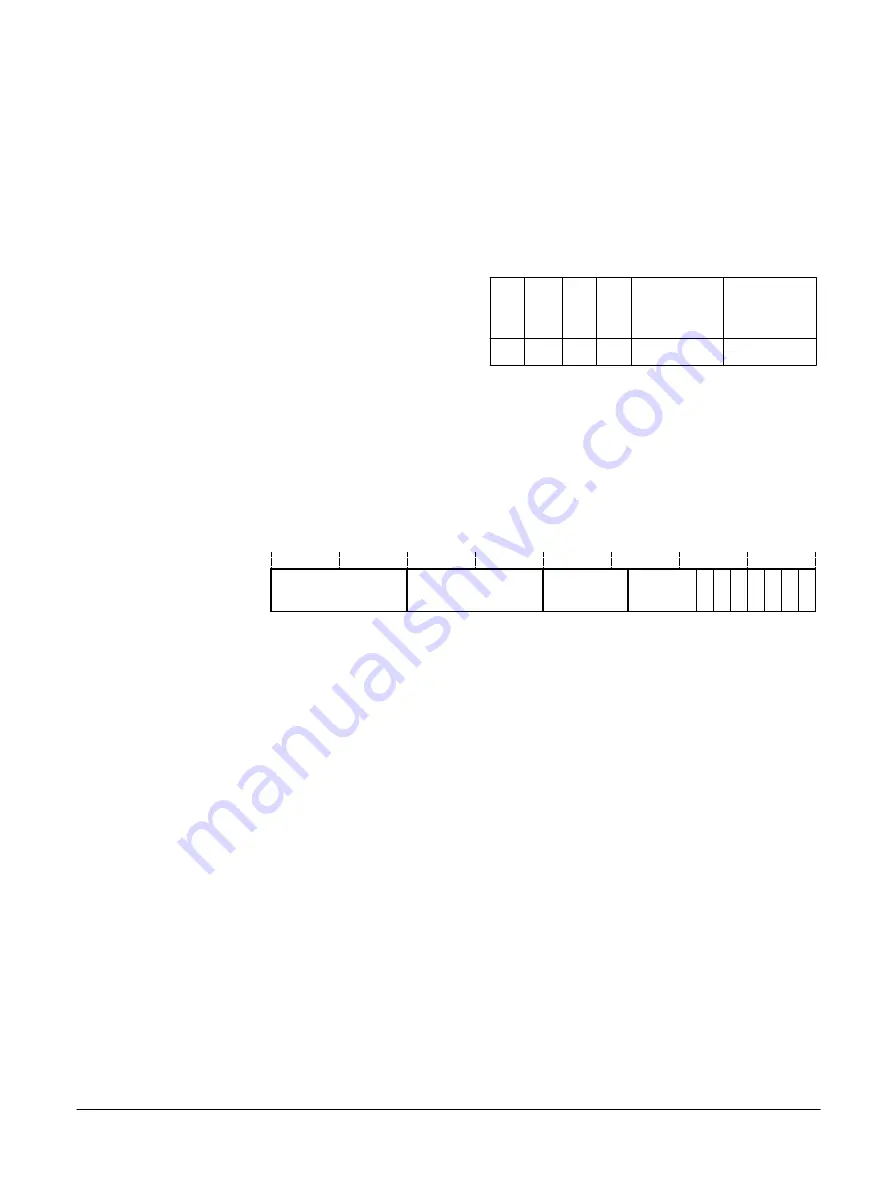

E

31

24 23

16 15

11 10

6 5 4 3 2 1 0

IMP

IDCODE

N

RES

0

DP X D C P

LC

7

Figure C10-4 PMCR_EL0 bit assignments

IMP, [31:24]

Implementer code:

0x41

Arm.

This is a read-only field.

IDCODE, [23:16]

Identification code:

0x0A

Cortex

‑

A35.

This is a read-only field.

N, [15:11]

Number of event counters.

0b00110

Six counters.

[10:7]

Reserved,

RES0

.

LC, [6]

Long cycle count enable. Determines which PMCCNTR_EL0 bit generates an overflow

recorded in PMOVSR[31]. The possible values are:

C10 PMU registers

C10.6 Performance Monitors Control Register, EL0

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

C10-704

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......