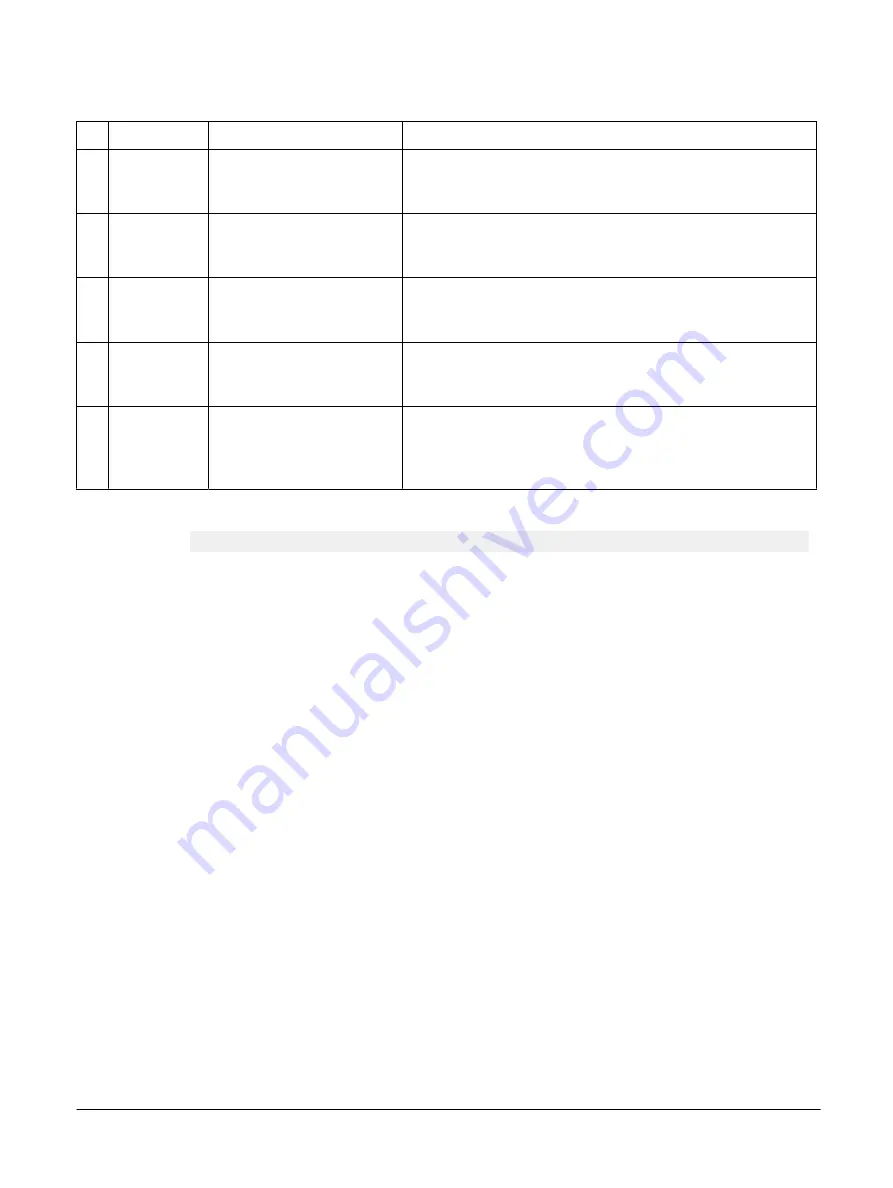

Table C10-5 PMU common events (continued)

Bit Event number Event mnemonic

Description

[4]

0x04

L1D_CACHE

L1 Data cache access:

1

This event is implemented.

[3]

0x03

L1D_CACHE_REFILL

L1 Data cache refill:

1

This event is implemented.

[2]

0x02

L1I_TLB_REFILL

L1 Instruction TLB refill:

1

This event is implemented.

[1]

0x01

L1I_CACHE_REFILL

L1 Instruction cache refill:

1

This event is implemented.

[0]

0x00

SW_INCR

Instruction architecturally executed, condition check pass - software

increment:

1

This event is implemented.

To access the PMCEID0_EL0:

MRS <Xt>, PMCEID0_EL0; Read Performance Monitor Common Event Identification Register 0

The PMCEID0_EL0 can be accessed through the external debug interface, offset

0xE20

.

C10 PMU registers

C10.7 Performance Monitors Common Event Identification Register 0, EL0

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

C10-710

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......