C10.10 Performance Monitors Configuration Register

The PMCFGR characteristics are:

Purpose

Contains PMU specific configuration data.

Usage constraints

The accessibility to the PMCFGR by condition code is:

Off

DLK OSLK EPMAD SLK Default

Error Error Error

Error

RO

RO

C2.2 External register access permissions to the PMU registers

condition codes.

Configurations

The PMCFGR is in the processor power domain.

Attributes

See

C10.9 Memory-mapped PMU register summary

.

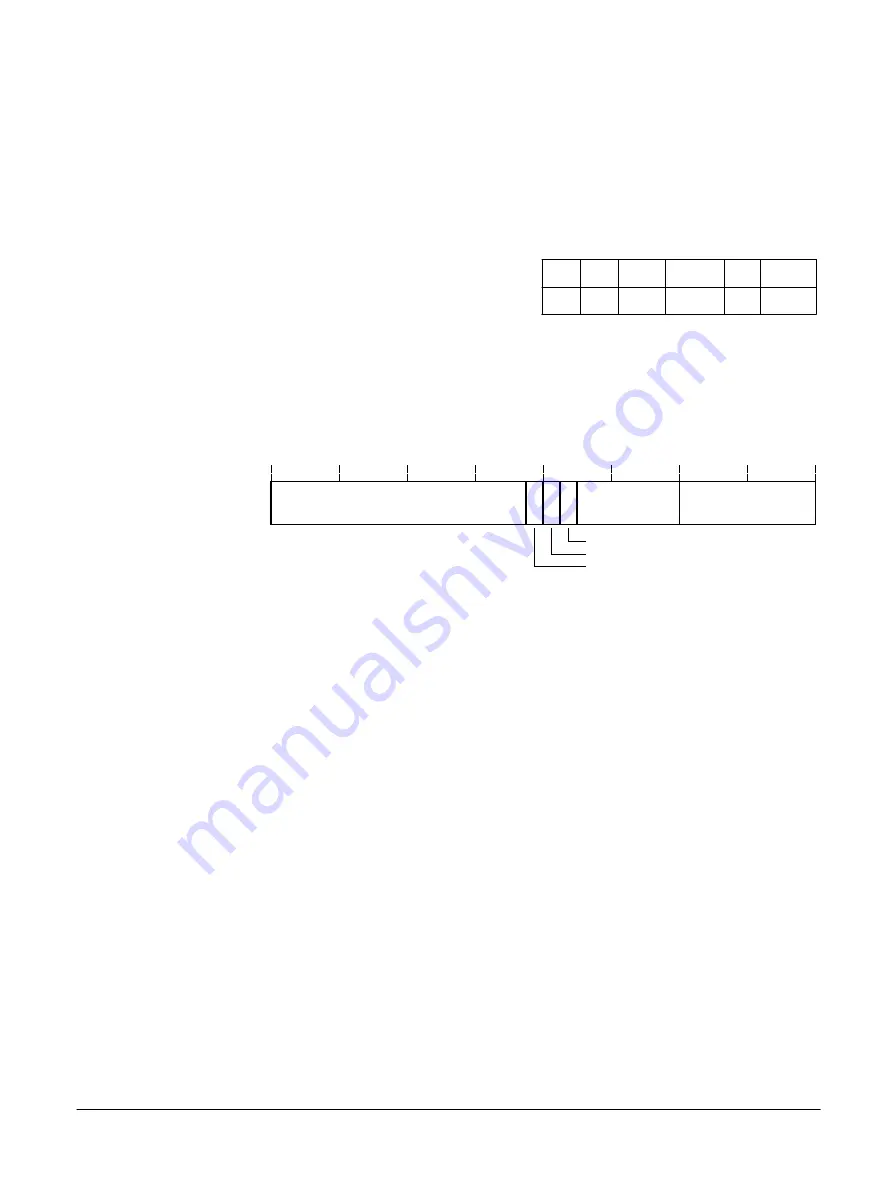

31

17 16 15 14 13

8 7

0

N

EX

CCD

CC

RES

0

Size

Figure C10-7 PMCFGR bit assignments

[31:17]

Reserved,

RES0

.

EX, [16]

Export supported. The value is:

1

Export is supported. PMCR_EL0.EX is read/write.

CCD, [15]

Cycle counter has pre-scale. The value is:

1

PMCR_EL0.D is read/write.

CC, [14]

Dedicated cycle counter supported. The value is:

1

Dedicated cycle counter is supported.

Size, [13:8]

Counter size. The value is:

0b111111

64-bit counters.

N, [7:0]

Number of event counters. The value is:

0x06

Six counters.

C10 PMU registers

C10.10 Performance Monitors Configuration Register

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

C10-717

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......