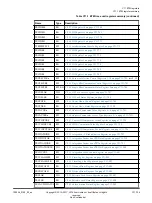

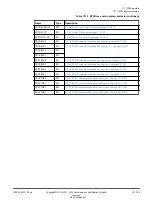

Chapter C11

ETM registers

This chapter describes the ETM registers.

It contains the following sections:

•

•

C11.2 Programming Control Register

•

•

C11.4 Trace Configuration Register

•

C11.5 Branch Broadcast Control Register

•

C11.6 Auxiliary Control Register

•

C11.7 Event Control 0 Register

•

C11.8 Event Control 1 Register

•

•

C11.10 Global Timestamp Control Register

•

C11.11 Synchronization Period Register

•

C11.12 Cycle Count Control Register

•

•

C11.14 ViewInst Main Control Register

•

C11.15 ViewInst Include-Exclude Control Register

•

C11.16 ViewInst Start-Stop Control Register

•

C11.17 Sequencer State Transition Control Registers 0-2

•

C11.18 Sequencer Reset Control Register

•

C11.19 Sequencer State Register

•

C11.20 External Input Select Register

•

C11.21 Counter Reload Value Registers 0-1

•

C11.22 Counter Control Register 0

•

C11.23 Counter Control Register 1

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

C11-731

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......