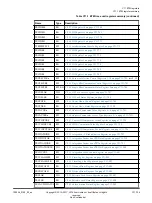

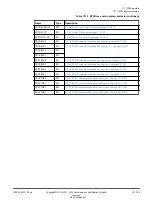

[5]

Reserved,

RES0

.

CCI, [4]

Enables cycle counting instruction trace. The possible values are:

0

Disables cycle counting instruction trace.

1

Enables cycle counting instruction trace.

BB, [3]

Enables branch broadcast mode. The possible values are:

0

Disables branch broadcast mode.

1

Enables branch broadcast mode.

[2:1]

Reserved,

RES0

.

[0]

Reserved,

RES1

.

The TRCCONFIGR can be accessed through the external debug interface, offset

0x010

.

C11 ETM registers

C11.4 Trace Configuration Register

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

C11-739

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......