C11.14 ViewInst Main Control Register

The TRCVICTLR characteristics are:

Purpose

Controls instruction trace filtering.

Usage constraints

• Accepts writes only when the trace unit is disabled.

• Returns stable data only when TRCSTATR.PMSTABLE==1.

• Must be programmed, particularly to set the value of the SSSTATUS bit, that sets the state of

the start-stop logic.

Configurations

Available in all configurations.

Attributes

See

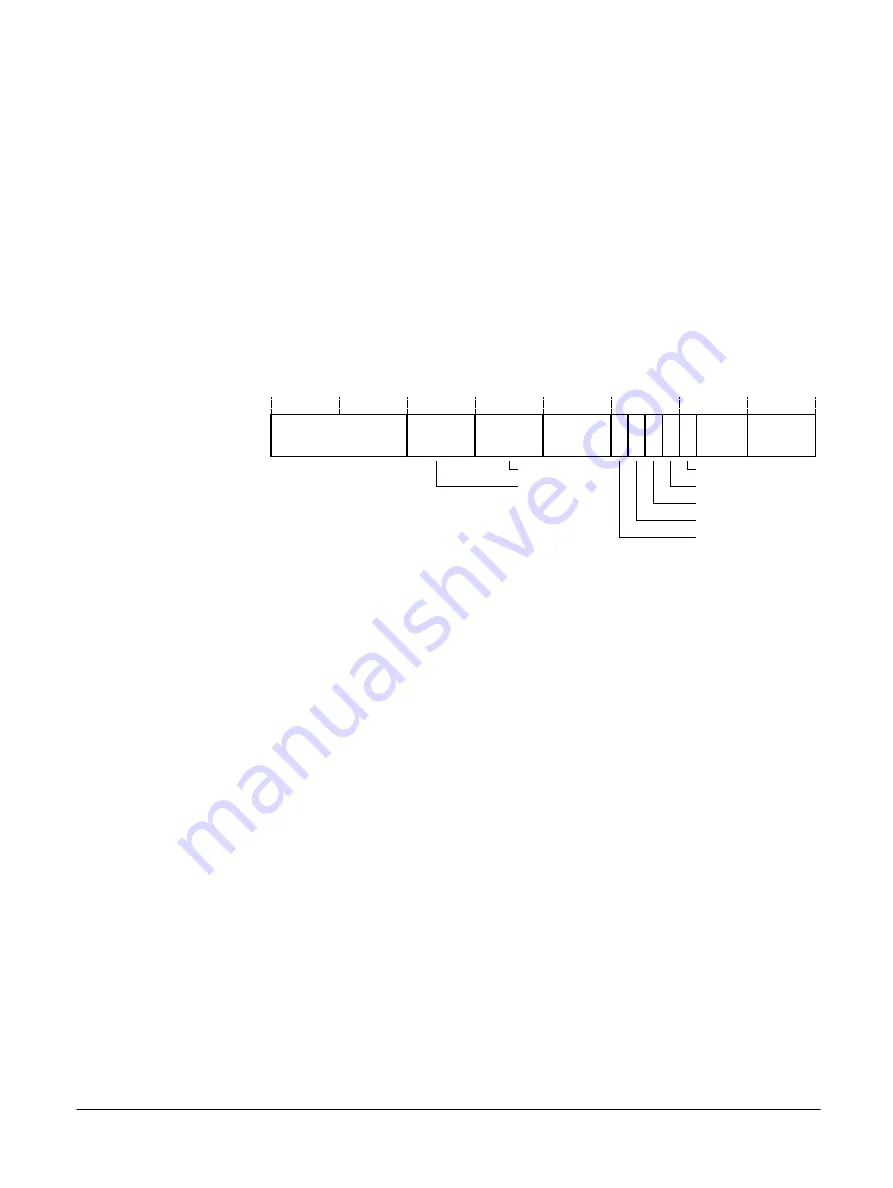

31

0

RES

0

7

8

9

10

11

15

12

16

19

20

23

24

RES

0

SSSTATUS

TRCRESET

TRCERR

EXLEVEL_S

EXLEVEL_NS

RES

0

6

3

4

SEL

TYPE

RES

0

Figure C11-13 TRCVICTLR bit assignments

[31:24]

Reserved,

RES0

.

EXLEVEL_NS, [23:20]

In Non-secure state, each bit controls whether instruction tracing is enabled for the

corresponding exception level:

0

Trace unit generates instruction trace, in Non-secure state, for exception level

n

.

1

Trace unit does not generate instruction trace, in Non-secure state, for exception level

n

.

The exception levels are:

Bit[20]

Exception level 0.

Bit[21]

Exception level 1.

Bit[22]

Exception level 2.

Bit[23]

RAZ/WI. Instruction tracing is not implemented for exception level 3.

EXLEVEL_S, [19:16]

In Secure state, each bit controls whether instruction tracing is enabled for the corresponding

exception level:

0

Trace unit generates instruction trace, in Secure state, for exception level

n

.

1

Trace unit does not generate instruction trace, in Secure state, for exception level

n

.

The exception levels are:

Bit[16]

Exception level 0.

C11 ETM registers

C11.14 ViewInst Main Control Register

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

C11-751

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......