C11.18 Sequencer Reset Control Register

The TRCSEQRSTEVR characteristics are:

Purpose

Resets the sequencer to state 0.

Usage constraints

• Accepts writes only when the trace unit is disabled.

• If the sequencer is used, you must program all sequencer state transitions with a valid event.

Configurations

Available in all configurations.

Attributes

See

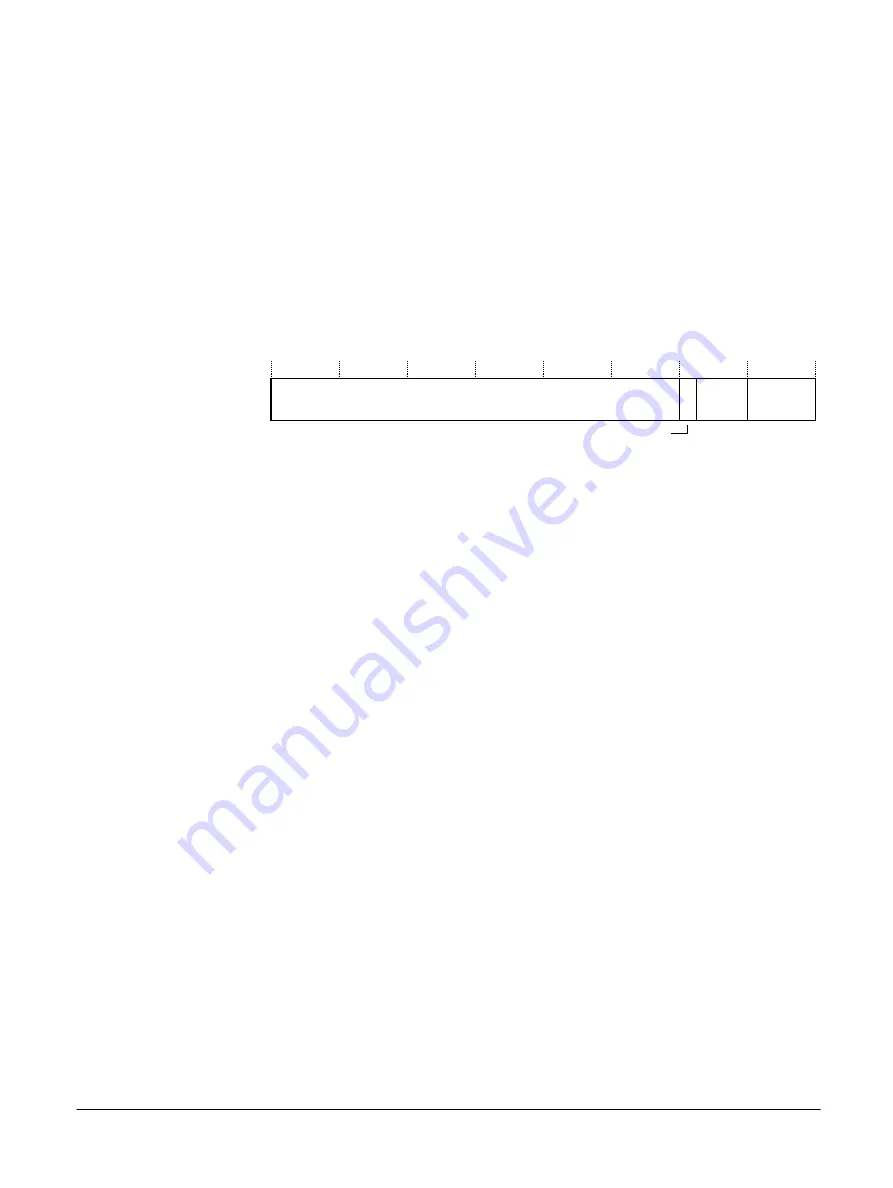

31

0

RES

0

RES

0

RESETSEL

8 7

4 3

6

RESETTYPE

Figure C11-17 TRCSEQRSTEVR bit assignments

[31:8]

Reserved,

RES0

.

RESETTYPE, [7]

Selects the resource type to move back to state 0:

0

Single selected resource.

1

Boolean combined resource pair.

[6:4]

Reserved,

RES0

.

RESETSEL, [3:0]

Selects the resource number, based on the value of RESETTYPE:

When RESETTYPE is 0, selects a single selected resource from 0-15 defined by bits[3:0].

When RESETTYPE is 1, selects a Boolean combined resource pair from 0-7 defined by

bits[2:0].

The TRCSEQRSTEVR can be accessed through the external debug interface, offset

0x118

.

C11 ETM registers

C11.18 Sequencer Reset Control Register

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

C11-757

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......