A.2

Processor configuration signals

The processor samples configuration signals only during cluster reset.

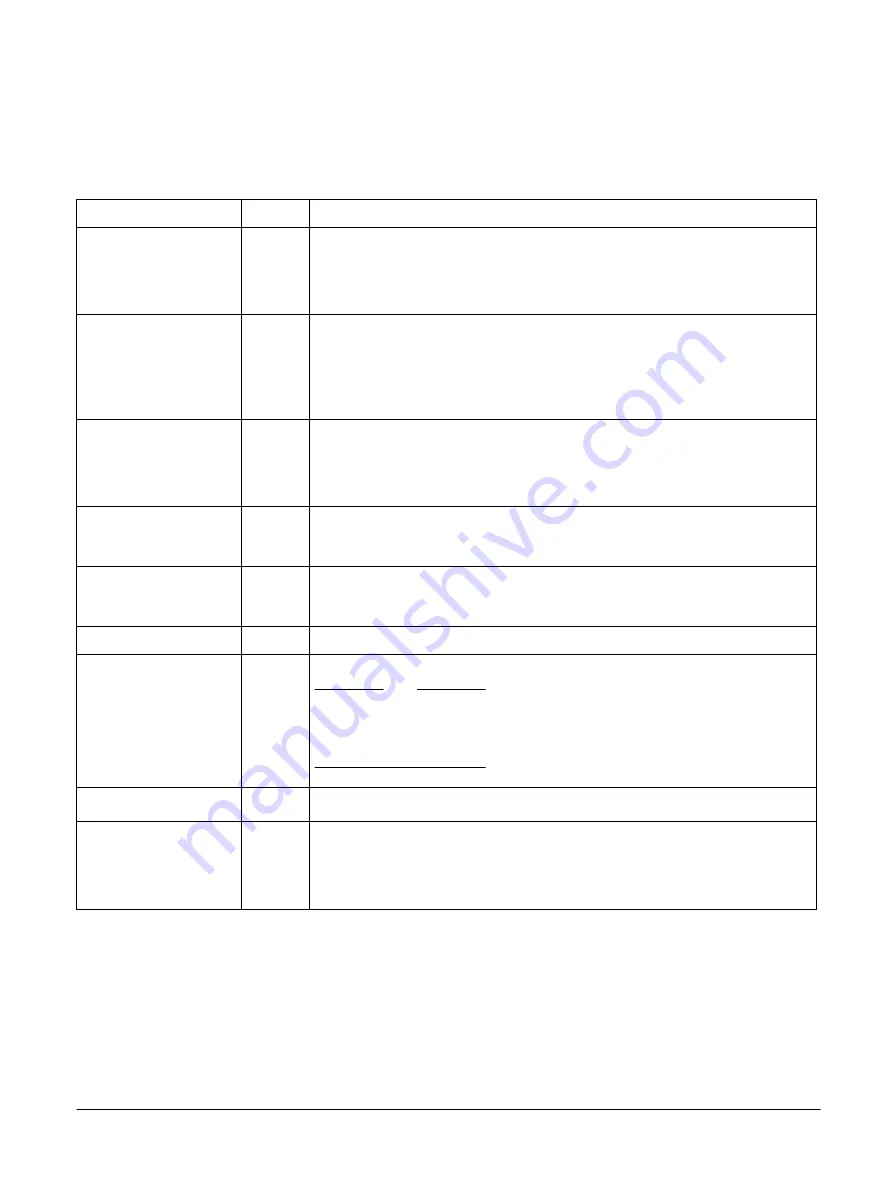

Table A-1 Processor configuration signals

Signal

Direction Description

AA64nAA32[CN:0]

Input

Register width state:

0

AArch32.

1

AArch64.

CFGEND[CN:0]

Input

Endianness configuration at reset. It sets the initial value of SCTLR_EL3.EE and

SCTR_S.EE:

0

LOW.

1

HIGH.

CFGTE[CN:0]

Input

Enabling T32 exceptions. It sets the initial value of SCTLR.TE:

0

LOW.

1

HIGH.

CLUSTERIDAFF1[7:0]

Input

Value read in MPIDR.Aff1.

This signal is sampled only during processor reset.

CLUSTERIDAFF2[7:0]

Input

Value read in MPIDR.Aff2.

This signal is sampled only during processor reset.

CP15SDISABLE2[CN:0]

Input

Disables write access to some Secure CP15 registers.

CRYPTODISABLE[CN:0]

Input

Disables the Cryptographic Extension.

Note

If a subset of cores in the processor is configured to include the Cryptographic Extension,

then

CRYPTODISABLE[CN:0]

is replaced with separate

CRYPTOxDISABLE

signals,

where x indicates the core that each signal relates to.

RVBARADDRx[39:2]

Input

Reset Vector Base Address for executing in 64-bit state.

VINITHI[CN:0]

Input

Location of the exception vectors at reset. It sets the initial value of SCTLR.V:

0

Exception vectors start at address

0x00000000

.

1

Exception vectors start at address

0xFFFF0000

.

Related information

B1.97 Multiprocessor Affinity Register

on page B1-315

B1.105 System Control Register

on page B1-331

B2.90 System Control Register, EL1

on page B2-525

A Signal Descriptions

A.2 Processor configuration signals

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

Appx-A-849

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......