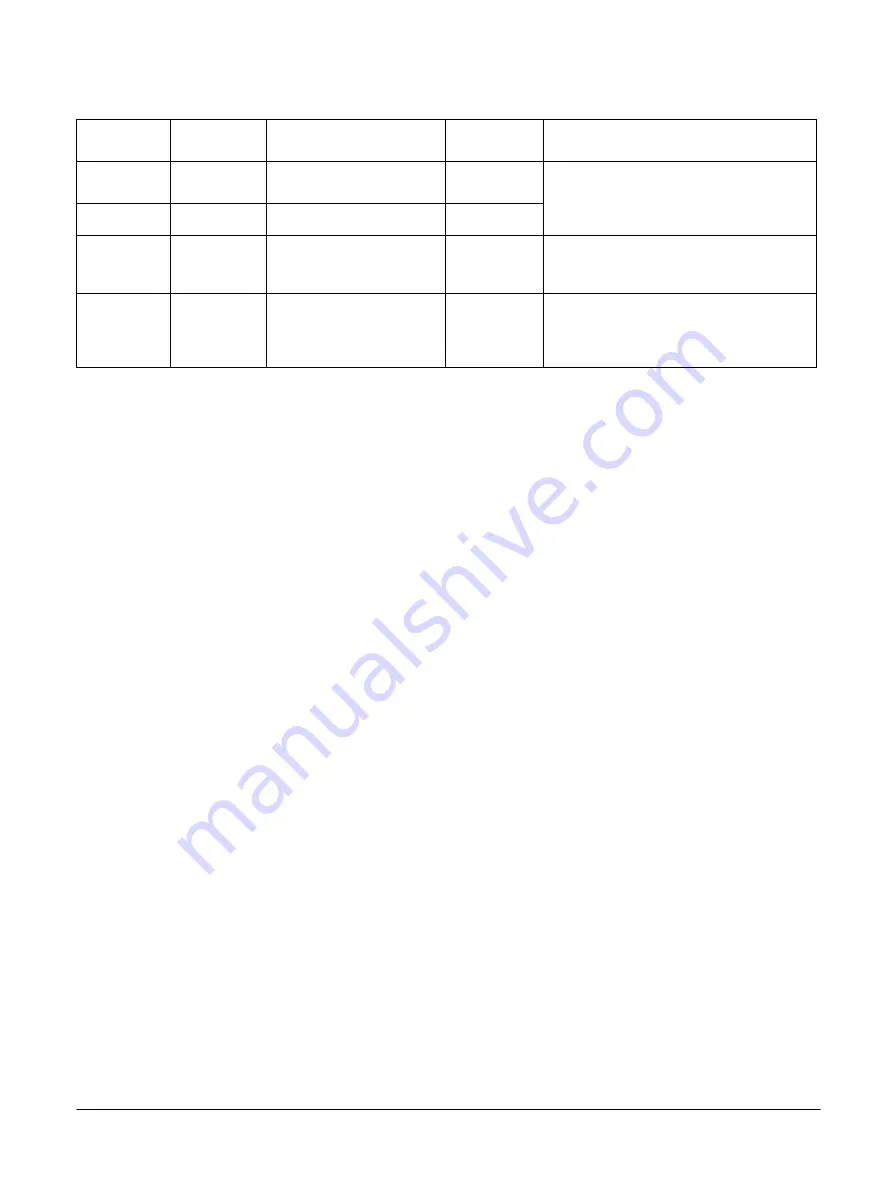

Table A5-2 Cache protection behavior of each RAM (continued)

RAM

Protection

type

Configuration option

Protection

granule

Correction behavior

SCU L1

duplicate tag

ECC, SECDED CPU_CACHE_PROTECTION 33 bits

The processor rewrites the tag with the correct

value and retries access. If the error is

uncorrectable then the processor invalidates the

tag.

L2 tag

ECC, SECDED SCU_CACHE_PROTECTION 32 bits

L2 victim

None

-

-

The victim RAM only serves as a performance

hint. It does not result in a functional failure if

the contents are incorrect.

L2 data

ECC, SECDED SCU_CACHE_PROTECTION 64 bits

The processor corrects the data inline and might

stall access for an additional cycle or two while

the correction takes place. After correction, the

processor might evict the line.

If a correctable ECC error occurs after the first data cache access of a load instruction that takes multiple

cycles to complete, and if one of the following conditions has taken place:

• A hardware breakpoint, watchpoint, or vector catch has been set since the first execution that is

triggered on re-execution.

• The page tables have been modified since the first execution. This resulted in an instruction or data

abort trap being taken on re-execution.

then the register file is updated with data that was successfully read before the correctable ECC error

occurred.

A5 Cache Behavior and Cache Protection

A5.7 About cache protection

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

A5-85

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......