C.1

Revisions

This section describes the technical changes between released issues of this book.

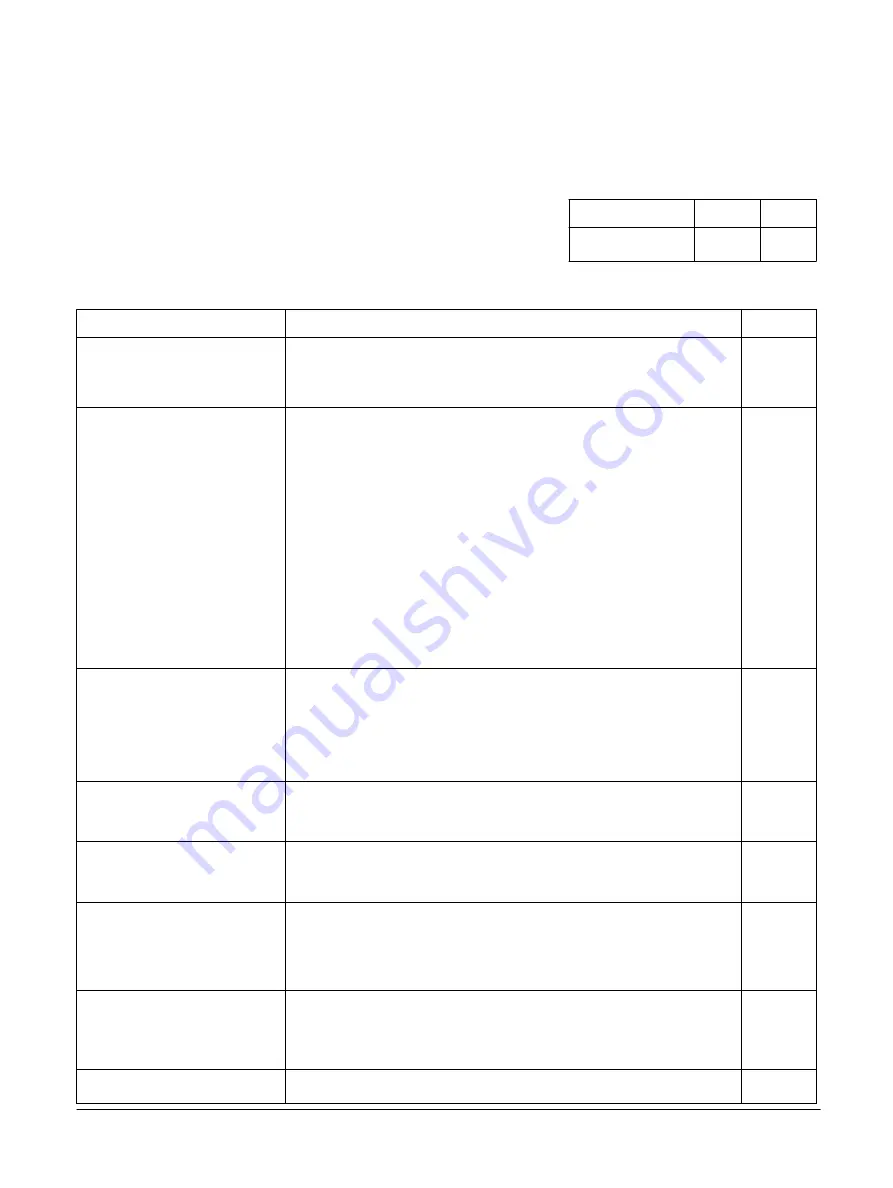

Table C-1 Issue 0000-00

Change

Location Affects

First release for r0p0. -

-

Table C-2 Issue 0001-00

Change

Location

Affects

Product name udpated from the

Mercury processor to the Cortex-

A35 processor.

Everywhere the product name is used.

All versions

First release for r0p1, revision

information updated.

B3.3 CPU Interface Identification Register

.

B3.8 VM CPU Interface Identification Register

.

C8.10 External Debug Peripheral Identification Register 1

.

C9.8 ROM Table Peripheral Identification Register 2

C10.14 Performance Monitors Peripheral Identification Register 2

.

C11.68 ETM Peripheral Identification Register 2

C12.8 CTI Peripheral Identification Register 2

.

r0p1

References to CP15DISABLE

signal removed.

B1.101 Primary Region Remap Register

B1.103 Reset Management Register

B1.105 System Control Register

All versions

CPUID/Way [20:18] bit field

description updated.

B1.44 CPU Memory Error Syndrome Register

B2.38 CPU Memory Error Syndrome Register, EL1

.

All versions

B1.94 L2 Memory Error Syndrome Register

B2.76 L2 Memory Error Syndrome Register, EL1

All versions

CCSIDR and CCSIDR_EL1

encodings table

updated.CPUID/Way [21:18] bit

field description updated.

B2.29 Cache Size ID Register, EL1

All versions

ICB [31:30] bit field description

updated.

LoUIS [23:21] bit field updated.

.

B2.30 Cache Level ID Register, EL1

.

All versions

DYNSDIS [11] bit updated.

B1.42 CPU Auxiliary Control Register

.

All versions

C Revisions

C.1 Revisions

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

Appx-C-892

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......