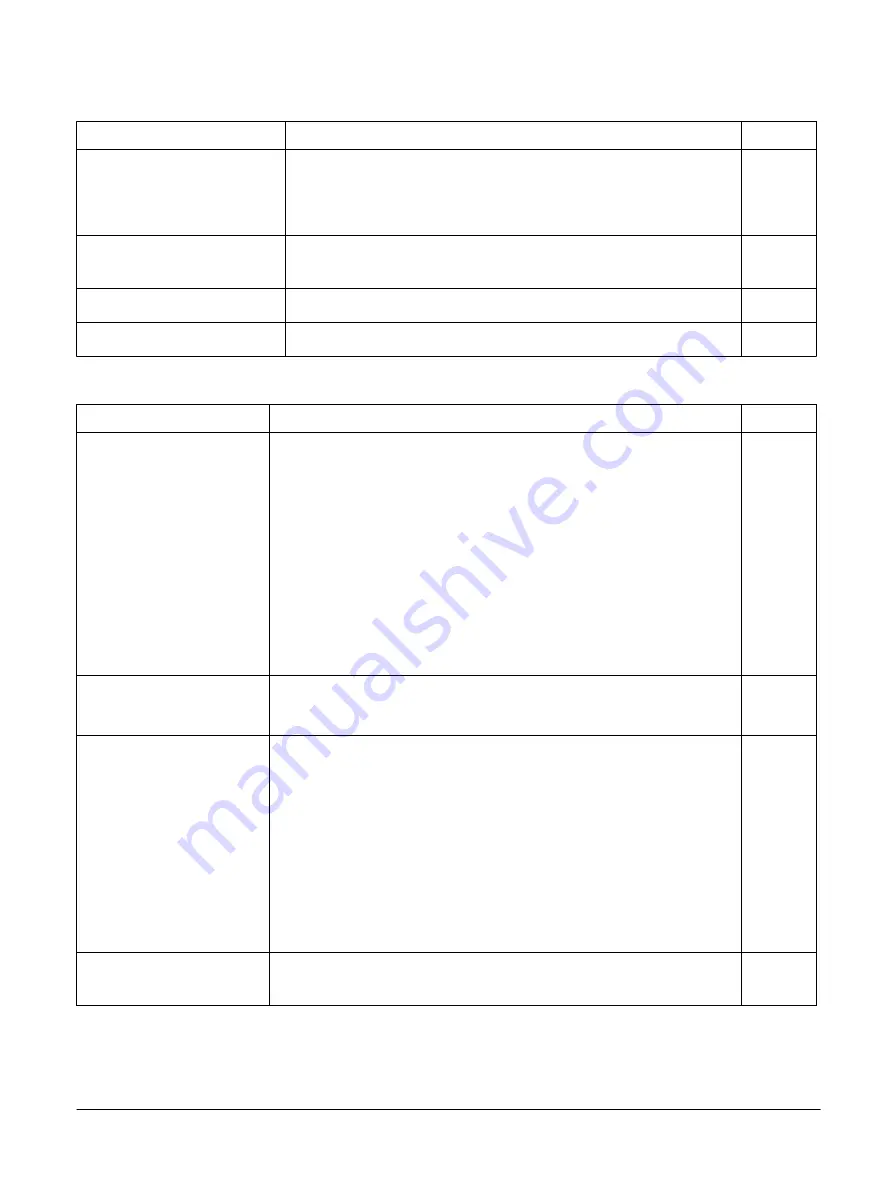

Table C-2 Issue 0001-00 (continued)

Change

Location

Affects

Several reset values updated in

summary tables.

.

B1.26 AArch32 Performance monitor registers

B2.10 AArch64 Performance monitor registers

All versions

PMU events added to PMU events

table.

C2.3 Performance monitoring events

.

All versions

DTAH [24] bit updated.

B2.36 CPU Auxiliary Control Register, EL1

All versions

ROM table for v7 added.

All versions

Table C-3 Issue 0002-00

Change

Location

Affects

First release for r0p2.

B3.3 CPU Interface Identification Register

B3.8 VM CPU Interface Identification Register

.

C8.10 External Debug Peripheral Identification Register 1

C9.8 ROM Table Peripheral Identification Register 2

.

C10.14 Performance Monitors Peripheral Identification Register 2

.

C11.68 ETM Peripheral Identification Register 2

C12.8 CTI Peripheral Identification Register 2

r0p2

Bits [9:0] updated in CPTR_EL3

and HCPTR.

B2.33 Architectural Feature Trap Register, EL3

B1.60 Hyp Architectural Feature Trap Register

All versions

References to internal memory-

mapped removed.

.

B1.97 Multiprocessor Affinity Register

.

B2.84 Multiprocessor Affinity Register, EL1

C7.1 AArch64 debug register summary

.

C8.1 Memory-mapped debug register summary

.

C10.1 AArch32 PMU register summary

.

C10.9 Memory-mapped PMU register summary

C12.1 Cross trigger register summary

All versions

nSEI, nREI, and nVSEI clarified

in GIC signals table.

All versions

C Revisions

C.1 Revisions

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

Appx-C-893

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......