A7.4

Memory type information exported from the processor

The processor makes attribute information about memory types available through signals for

interconnects or bus protocols that require such information.

Some interconnects or bus protocols might require more information about the memory type and, for

these cases, the cluster exports the memory attribute information from the translation tables stored in the

TLB. These signals are for information only, and do not form part of the AXI, ACE, or CHI protocols.

• In an AXI or ACE configuration, there is a

RDMEMATTR

bus for the read channel and a

WRMEMATTR

bus for the write channel.

• In a CHI configuration, there is a single

REQMEMATTR

bus.

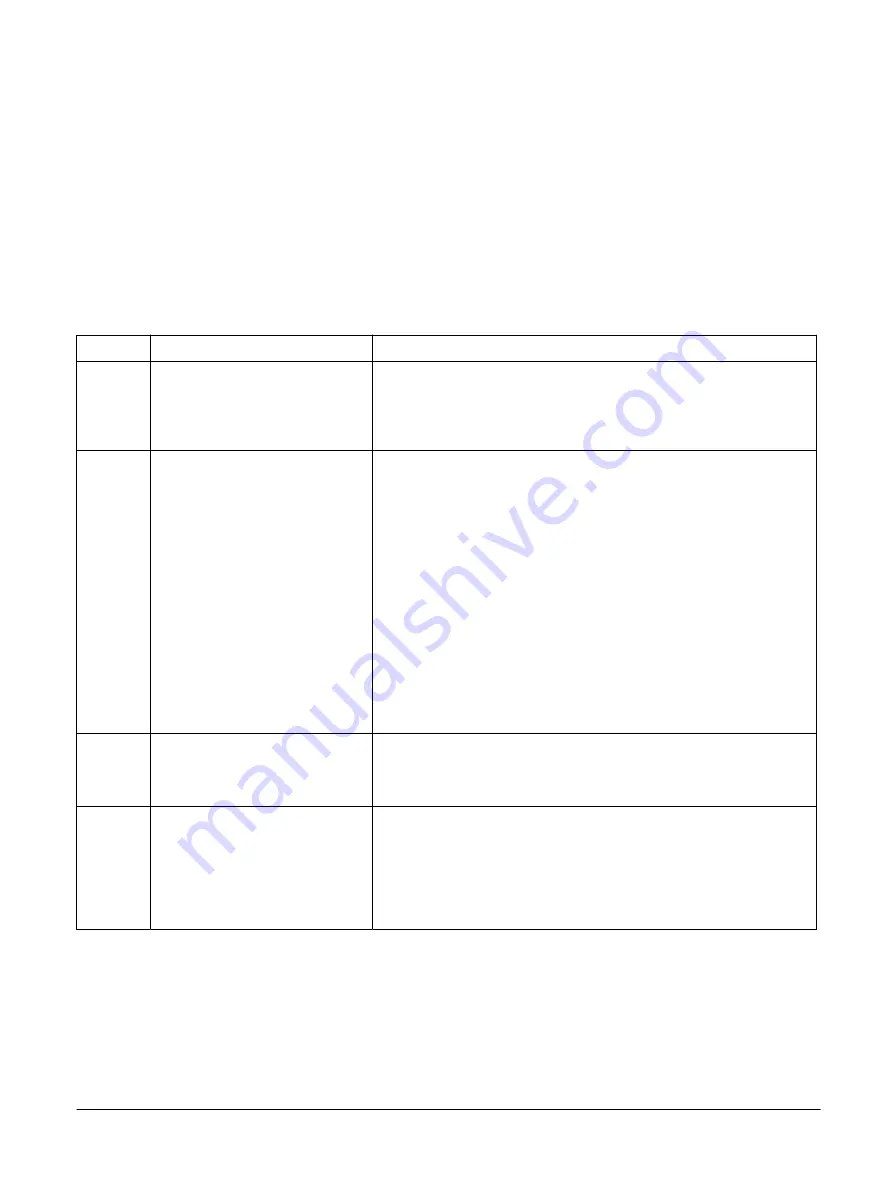

Table A7-2 Bus encoding for memory attributes

Bits

Encoding

Notes

[7]

Outer shareable.

Always set for device memory or

memory that is both inner and outer

non-cacheable.

Shareability information is not recorded in the L1 data cache for

implementations that use the mini-SCU.

WRMEMATTR[7]

is

0b0

for L1 data

cache evictions in these implementations.

[6:3]

Outer memory type, or device type.

If bits[1:0] indicate Device, then:

0b0000

nGnRnE.

0b0100

nGnRE.

0b1000

nGRE.

0b1100

GRE.

If bits[1:0] indicate Normal, then:

0b0100

NC.

0b10RW

WT.

0b11RW

WB.

Where

R

is read allocate hint,

W

is

write allocate hint.

If an Armv7 architecture operating system runs on the processor, the Device

memory type matches the nGnRE encoding and the Strongly-Ordered memory

type matches the nGnRnE memory type.

Outer read allocate hint information is not recorded in the L1 or L2 data caches.

WRMEMATTR[4]

and

REQMEMATTR[4]

are set to

0b1

for data cache

evictions.

[2]

Inner shareable.

Anything with bit[7] set must also

have bit[2] set.

Shareability information is not recorded in the L1 data cache for

implementations that use the mini-SCU.

WRMEMATTR[2]

is

0b0

for L1 data

cache evictions in these implementations.

[1:0]

Inner memory type:

0b00

Device.

0b01

NC.

0b10

WT.

0b11

WB.

A7 L2 Memory System

A7.4 Memory type information exported from the processor

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

A7-102

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......