A8.3

AXI transactions

The processor generates only a subset of all possible AXI transactions on the AXI master interface.

The processor does not generate any FIXED bursts and all WRAP bursts fetch a complete cache line

starting with the critical word first. A burst does not cross a cache line boundary.

The cache linefill fetch length is always 64 bytes.

For WriteBack transfers the supported transfers are:

• WRAP 4 128-bit for read transfers (linefills).

• INCR 4 128-bit for write transfers (evictions).

• INCR N (N:1, 2, or 4) 128-bit write transfers (read allocate).

For Non-cacheable transactions:

• WRAP 4 128-bit for read transfers.

• INCR N (N:1, 2, or 4) 128-bit for write transfers.

• INCR N (N:1, 2, or 4) 128-bit for read transfers.

• INCR 1 32-bit, 64-bit, and 128-bit for read transfers.

• INCR 1 8-bit, 16-bit, 32-bit, 64-bit, and 128-bit for write transfers.

• INCR 1 8-bit, 16-bit, 32-bit, 64-bit, and 128-bit for exclusive write transfers.

• INCR 1 8-bit, 16-bit, 32-bit, 64-bit, and 128-bit for exclusive read transfers.

For Device transactions:

• INCR N (N:1, 2, or 4) 128-bit read transfers.

• INCR N (N:1, 2, or 4) 128-bit write transfers.

• INCR 1 8-bit, 16-bit, 32-bit, 64-bit, and 128-bit read transfers.

• INCR 1 8-bit, 16-bit, 32-bit, 64-bit, and 128-bit write transfers.

• INCR 1 8-bit, 16-bit, 32-bit, 64-bit, and 128-bit exclusive read transfers.

• INCR 1 8-bit, 16-bit, 32-bit, 64-bit, and 128-bit exclusive write transfers.

For translation table walk transactions INCR 1 32-bit, and 64-bit read transfers.

The following points apply to AXI transactions:

• WRAP bursts are only 128-bit.

• INCR 1 can be any size for read or write.

• INCR burst, more than one transfer, are only 128-bit.

• No transaction is marked as FIXED.

• Write transfers with none, some, or all byte strobes LOW can occur.

External memory accesses generate the following transactions in an implementation configured with an

AXI master interface.

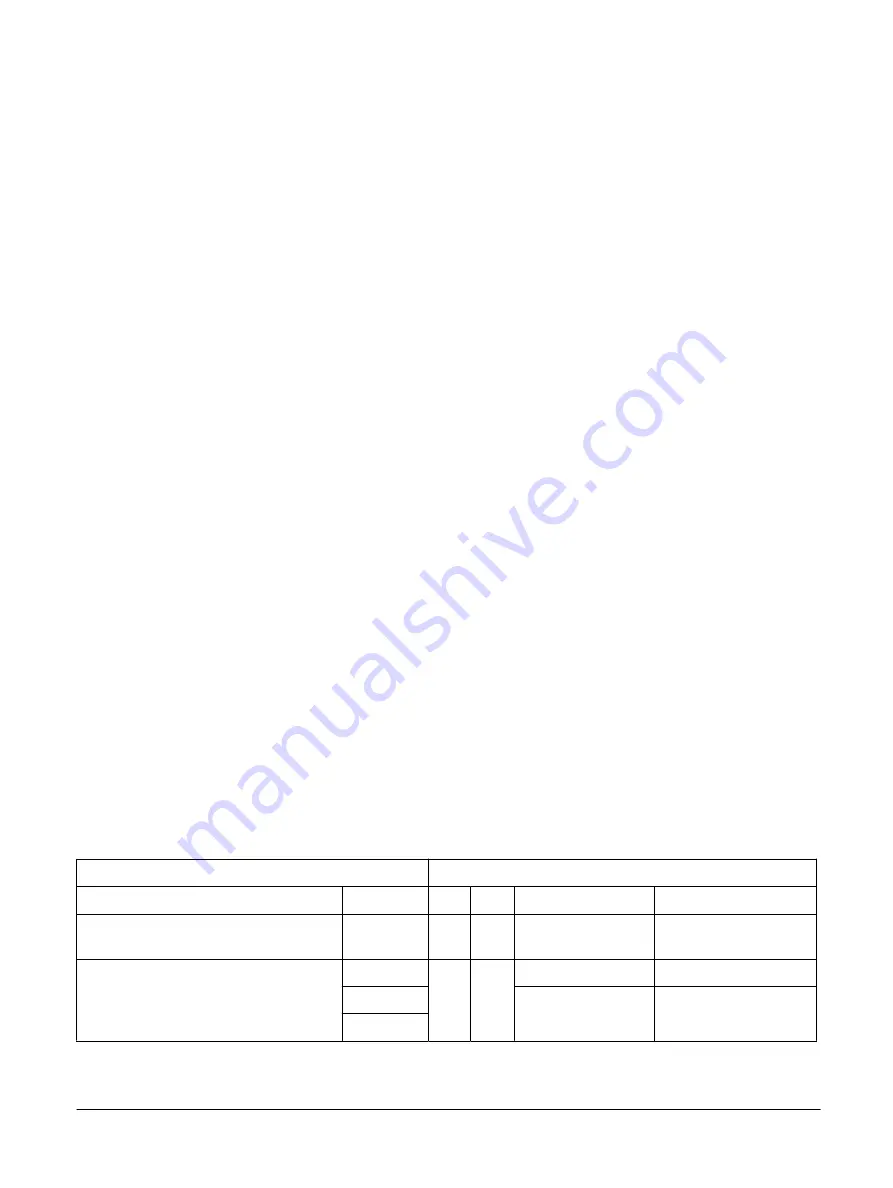

Table A8-2 AXI transactions

Attributes

AXI transaction

Memory type

Shareability Load Store Load exclusive

Store exclusive

Device

-

Read Write Read with

ARLOCKM

set HIGH

Write with

AWLOCKM

set HIGH

Normal, inner Non-cacheable, outer Non-

cacheable

Non-shared

Read Write Read

Write

Inner-shared

Read with

ARLOCKM

set HIGH

Write with

ARLOCKM

set

HIGH

Outer-shared

A8 AXI Master Interface

A8.3 AXI transactions

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

A8-108

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......