A8.4

Attributes of the AXI master interface

The table lists the possible values for the read and write issuing capabilities if the processor includes four

cores.

n

Number of cores.

m

1 if the processor is configured for the ACP interface, 0 if it is not.

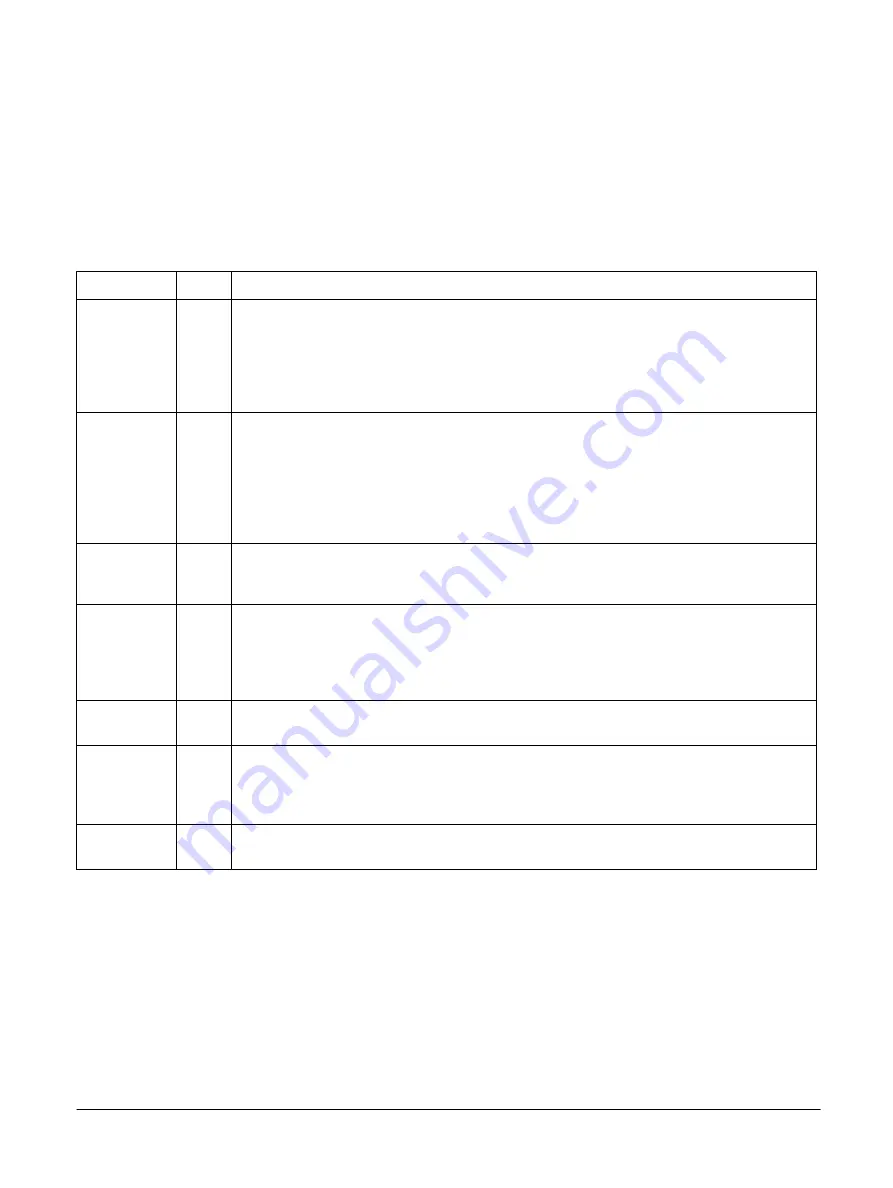

Table A8-3 AXI master interface attributes

Attribute

Value

Comments

Write issuing

capability

16

The cluster can issue a maximum of 16 writes:

•

Up to 16 writes to Normal memory that is both inner and outer write-back cacheable.

•

Up to 15 writes to all other memory types, including Device, Normal non-cacheable, and Write-

through.

Any mix of memory types is possible, and each write can be a single write or a write burst.

Read issuing

capability

8n + 4m 8 for each core in the cluster including up to:

•

8 data linefills.

•

4 non-cacheable or Device data reads.

•

1 non-cacheable TLB page-walk read.

•

3 instruction linefills.

If an ACP is configured, up to 4 ACP linefill requests can be generated.

Exclusive thread

capability

n

Each core can have 1 exclusive access sequence in progress.

Write ID

capability

16

The maximum number of outstanding write IDs is 16. This is the same as the maximum number of

outstanding writes.

Only Device memory types with nGnRnE or nGnRE can have more than one outstanding transaction with

the same AXI ID. All other memory types use a unique AXI ID for every outstanding transaction.

Write ID width

5

The ID encodes the source of the memory transaction. See

Table A9-7 Encoding for AWIDM[4:0]

.

Read ID

capability

8n + 4m 8 for each core in the processor and 4 for the ACP.

Only Device memory types with nGnRnE or nGnRE can have more than one outstanding transaction with

the same AXI ID. All other memory types use a unique AXI ID for every outstanding transaction.

Read ID width

6

The ID encodes the source of the memory transaction. See

Table A9-8 Encoding for ARIDM[5:0]

.

In the following table, nn is the core number

0b00

,

0b01

,

0b10

, or

0b11

.

A8 AXI Master Interface

A8.4 Attributes of the AXI master interface

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

A8-110

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......