A10.4

CHI channel properties

You can configure the processor to use the CHI protocol for the master memory interface

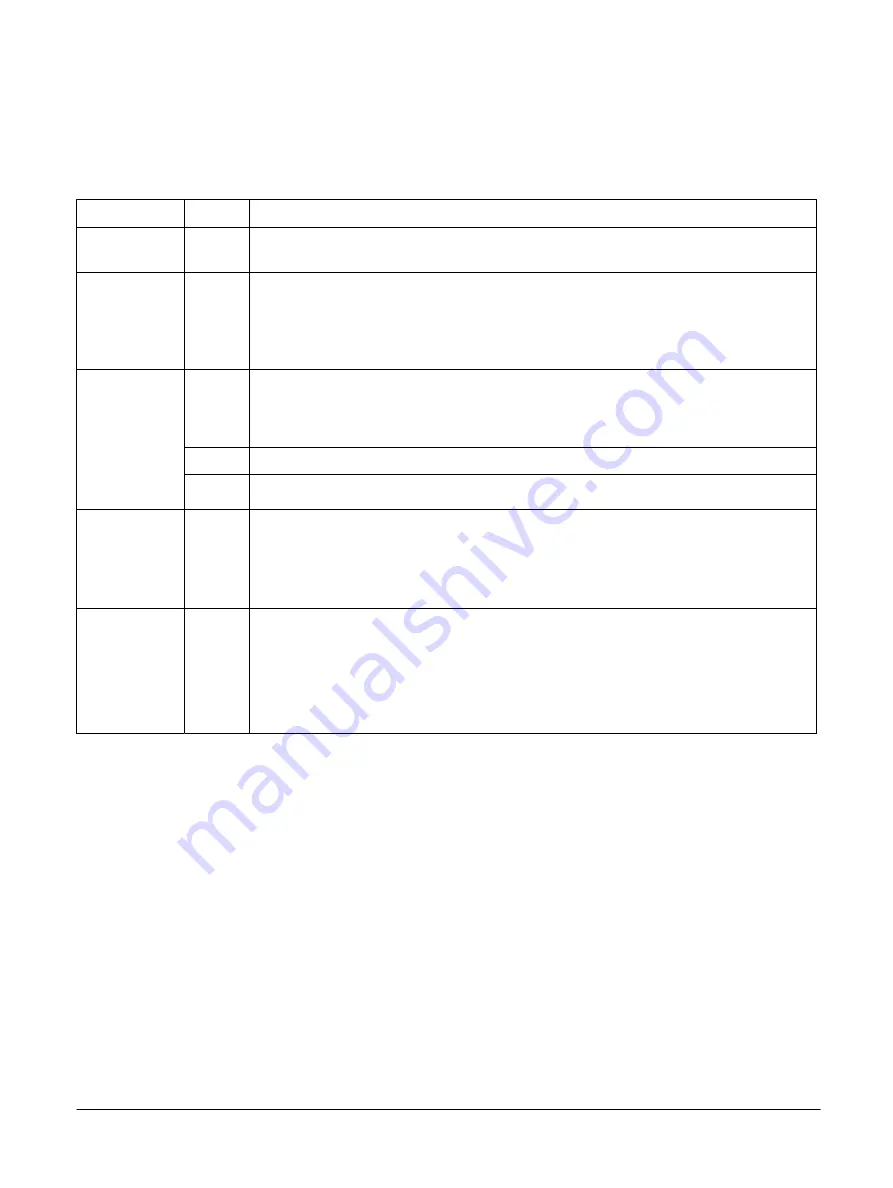

Table A10-4 CHI channel properties

Property

Value

Comment

Snoop acceptance

capability

10

The SCU can accept and process a maximum of 10 snoop requests from the system.

DVM acceptance

capability

4

The SCU can accept and process a maximum of four DVM transactions from the system. Each of

these four transactions can be a two part DVM message.

The interconnect must be configured to never send more than four DVM messages to a Cortex

‑

A35

processor, otherwise the system might deadlock.

Snoop latency

Hit

When there is a hit in L2 cache, the best case for response and data is 11 processor cycles. When there

is a miss in L2 cache and a hit in L1 cache, the best case for response and data is 14 processor cycles.

Latencies can be higher if hazards occur or if there are not enough buffers to absorb requests.

Miss

Best case six processor cycles when the SCU duplicate tags and L2 tags indicate the miss.

DVM

The cluster takes a minimum of six cycles to provide a response to DVM packets.

Snoop filter

Supported The cluster provides support for an external snoop filter in an interconnect. It indicates when clean

lines are evicted from the processor by sending Evict transactions on the CHI write channel. However,

there are some cases where incorrect software can prevent an Evict transaction from being sent,

therefore you must ensure that any external snoop filter is built to handle a capacity overflow that

sends a back-invalidation to the processor if it runs out of storage.

Supported

transactions

-

All transactions described by the CHI protocol:

•

Are accepted on the CHI master interface from the system.

•

Can be produced on the CHI master interface except:

— ReadClean.

— WriteBackPtl.

— WriteCleanPtl.

Related information

Arm® AMBA® 5 CHI Protocol Specification

A10 CHI Master Interface

A10.4 CHI channel properties

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

A10-130

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......