B1.17

c14 registers

The processor can access different 32-bit wide system registers. Registers where CRn has the value

fourteen are called c14 registers.

The following table shows the CP15 system registers when the processor is in AArch32 state and the

value of CRn is c14. See the

Arm

®

Architecture Reference Manual Armv8, for Armv8-A architecture

profile

for more information.

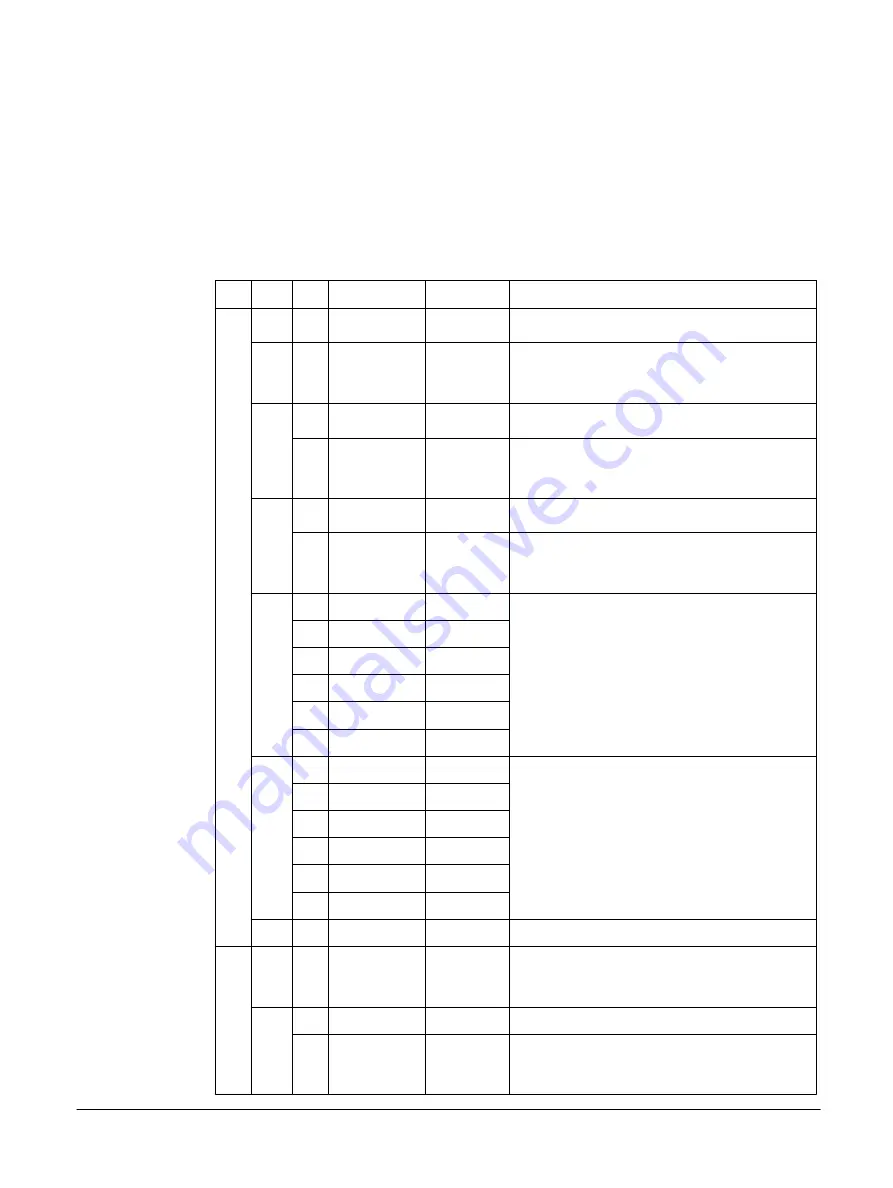

Table B1-16 c14 register summary

Op1 CRm Op2 Name

Reset

Description

0

c0

0

CNTFRQ

UNK

Timer Counter Frequency Register

c1

0

CNTKCTL

-

Timer Control Register

The reset value for bits[9:8, 2:0] is

0b00000

.

c2

0

CNTP_TVAL

UNK

Physical Timer Value Register

1

CNTP_CTL

-

Physical Timer Control Register

The reset value for bit[0] is 0.

c3

0

CNTV_TVAL

UNK

Virtual Timer TimerValue Register

1

CNTV_CTL

-

Counter-timer Virtual Timer Control Register

The reset value for bit[0] is 0.

c8

0

PMEVCNTR0

UNK

Performance Monitor Event Count Registers

1

PMEVCNTR1

UNK

2

PMEVCNTR2

UNK

3

PMEVCNTR3

UNK

4

PMEVCNTR4

UNK

5

PMEVCNTR5

UNK

c12

0

PMEVTYPER0 UNK

Performance Monitor Event Type Registers

1

PMEVTYPER1 UNK

2

PMEVTYPER2 UNK

3

PMEVTYPER3 UNK

4

PMEVTYPER4 UNK

5

PMEVTYPER5 UNK

c15

7

PMCCFILTR

0x00000000

Performance Monitor Cycle Count Filter Register.

4

c1

0

CNTHCTL

-

Timer Control Register (EL2)

The reset value for bit[2] is 0 and for bits[1:0] is

0b11

.

c2

0

CNTHP_TVAL UNK

Physical Timer TimerValue (EL2)

1

CNTHP_CTL

-

Physical Timer Control Register (EL2)

The reset value for bit[0] is 0.

B1 AArch32 system registers

B1.17 c14 registers

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

B1-173

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......