B1.99

Normal Memory Remap Register

The NMRR characteristics are:

Purpose

Provides additional mapping controls for memory regions that are mapped as Normal memory

by their entry in the PRRR.

Usage constraints

This register is accessible as follows:

EL0

(NS)

EL0

(S)

EL1

(NS)

EL1

(S)

EL2 EL3

(SCR.NS = 1)

EL3

(SCR.NS = 0)

-

-

RW

RW RW RW

RW

The register is:

• Used in conjunction with the PRRR.

• Not accessible when using the Long-descriptor translation table format.

Configurations

If EL3 is using AArch32, there are separate Secure and Non-secure instances of this register.

If EL3 is using AArch32, write access to NMRR(S) is disabled when the

CP15SDISABLE2

signal is asserted HIGH.

The Non-secure NMRR is architecturally mapped to the AArch64 MAIR_EL1[63:32] register

when TTBCR.EAE==0. See

B2.77 Memory Attribute Indirection Register, EL1

.

The Secure NMRR is mapped to the AArch64 MAIR_EL3[63:32] register when

TTBCR.EAE==0. See

B2.79 Memory Attribute Indirection Register, EL3

.

Attributes

NMRR is a 32-bit register when TTBCR.EAE is 0.

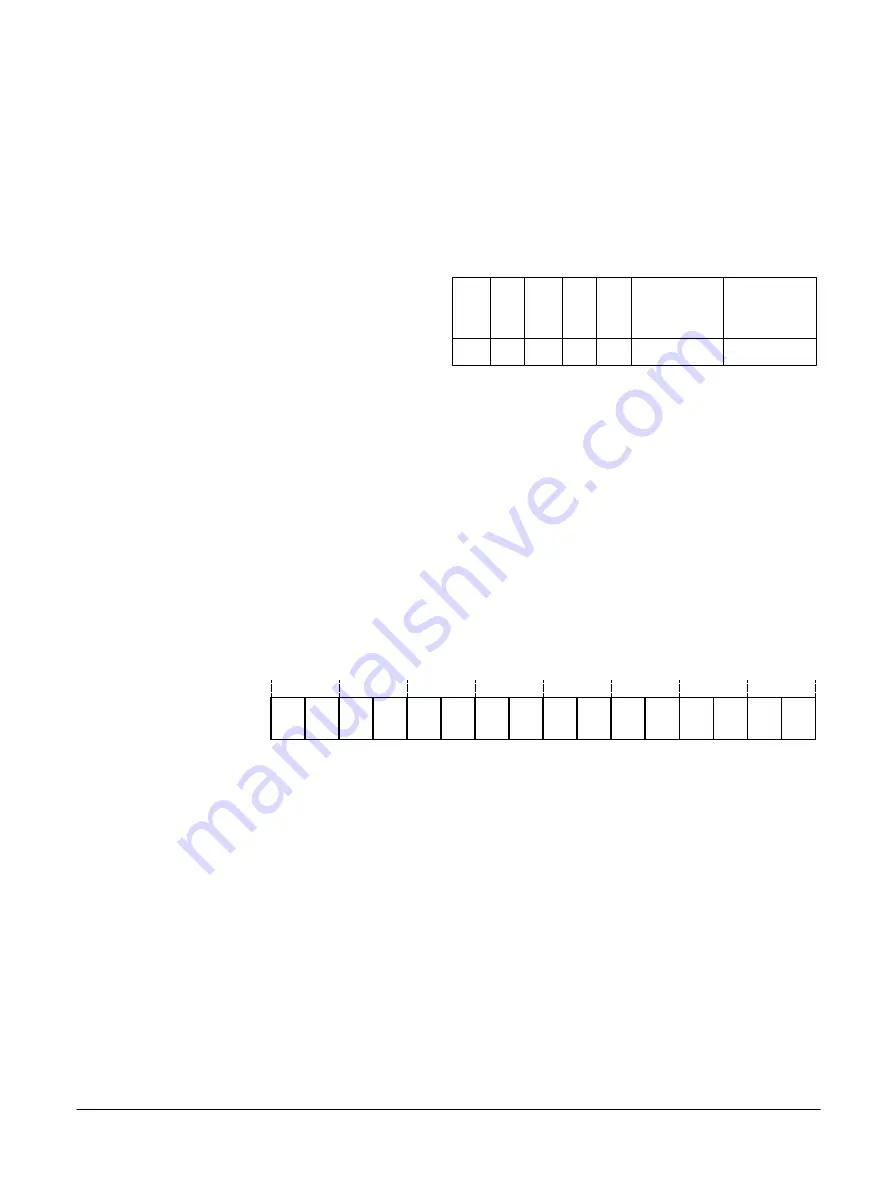

31 30 29 28 27 26 25 24 23

20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

IR0

IR1

IR7

IR6

IR5

IR4

IR3

IR2

22 21

OR0

OR1

OR7 OR6 OR5 OR4 OR3 OR2

Figure B1-53 NMRR bit assignments

ORn, [2n+17:2n+16]

Outer Cacheable property mapping for memory attributes

n

, where n is 0-7, if the region is

mapped as Normal memory by the PRRR.TR

n

entry.

n

is the value of the TEX[0], C and B bits,

Memory attributes and the n value for the PRRR field descriptions

. The

possible values of this field are:

0b00

Region is Non-cacheable.

0b01

Region is Write-Back, Write-Allocate.

0b10

Region is Write-Through, no Write-Allocate.

0b11

Region is Write-Back, no Write-Allocate.

IRn, [2n+1:2n]

Inner Cacheable property mapping for memory attributes

n

, where n is 0-7, if the region is

mapped as Normal Memory by the PRRR.TR

n

entry.

n

is the value of the TEX[0], C and B bits,

Memory attributes and the n value for the PRRR field descriptions

. The

possible values of this field are the same as those given for the OR

n

field.

B1 AArch32 system registers

B1.99 Normal Memory Remap Register

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

B1-319

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......