B2.3

AArch64 Exception handling registers

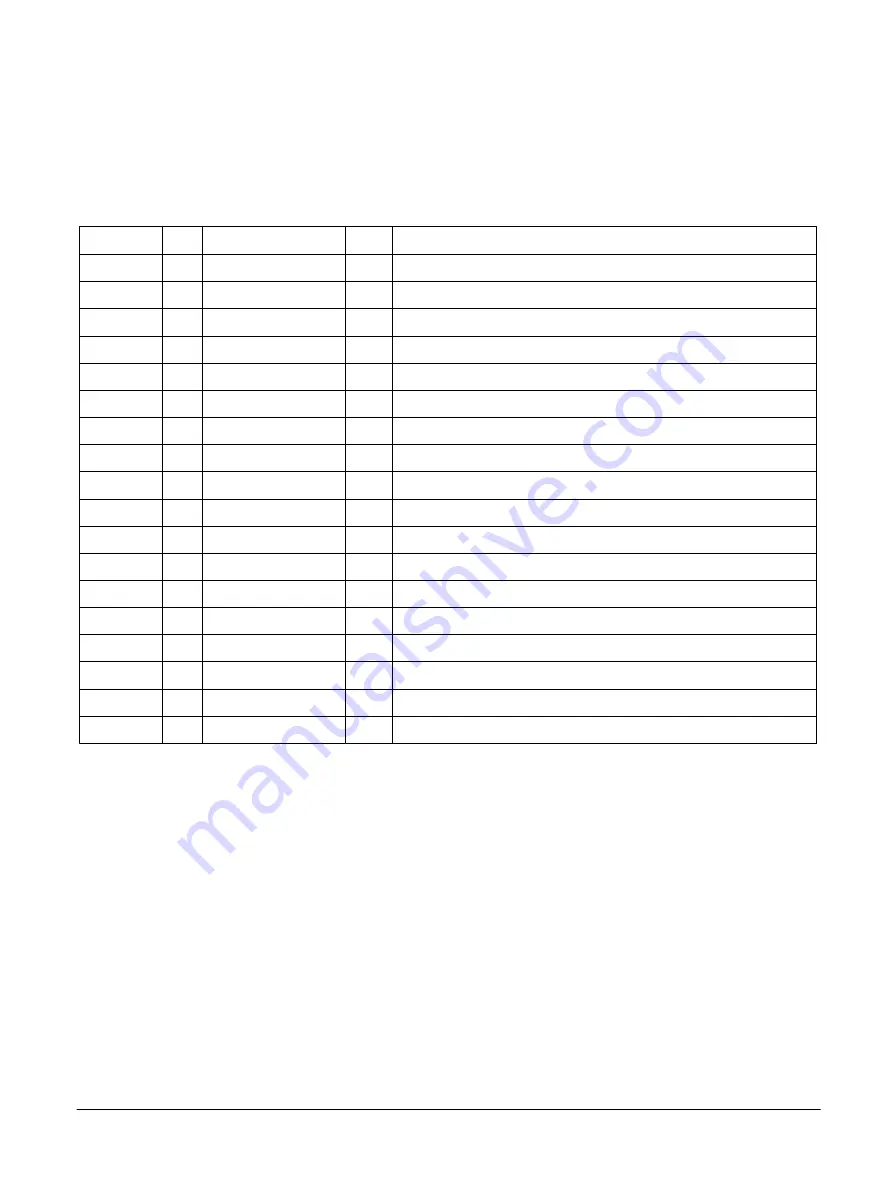

The following table shows the fault handling registers in AArch64 state.

Bits[63:32] are reset to

0x00000000

for all 64-bit registers in the table.

Table B2-2 AArch64 exception handling registers

Name

Type Reset

Width Description

AFSR0_EL1 RW

0x00000000

32

B2.22 Auxiliary Fault Status Register 0, EL1, EL2, and EL3

AFSR1_EL1 RW

0x00000000

32

B2.23 Auxiliary Fault Status Register 1, EL1, EL2, and EL3

ESR_EL1

RW

UNK

32

B2.41 Exception Syndrome Register, EL1

IFSR32_EL2 RW

UNK

32

B2.69 Instruction Fault Status Register, EL2

AFSR0_EL2 RW

0x00000000

32

B2.22 Auxiliary Fault Status Register 0, EL1, EL2, and EL3

AFSR1_EL2 RW

0x00000000

32

B2.23 Auxiliary Fault Status Register 1, EL1, EL2, and EL3

ESR_EL2

RW

UNK

32

B2.42 Exception Syndrome Register, EL2

AFSR0_EL3 RW

0x00000000

32

B2.22 Auxiliary Fault Status Register 0, EL1, EL2, and EL3

AFSR1_EL3 RW

0x00000000

32

B2.23 Auxiliary Fault Status Register 1, EL1, EL2, and EL3

ESR_EL3

RW

UNK

32

B2.43 Exception Syndrome Register, EL3

FAR_EL1

RW

UNK

64

B2.44 Fault Address Register, EL1

FAR_EL2

RW

UNK

64

B2.45 Fault Address Register, EL2

HPFAR_EL2 RW

0x0000000000000000

64

B2.49 Hypervisor IPA Fault Address Register, EL2

FAR_EL3

RW

UNK

64

B2.46 Fault Address Register, EL3

VBAR_EL1 RW

UNK

64

B2.100 Vector Base Address Register, EL1

ISR_EL1

RO

UNK

32

B2.72 Interrupt Status Register, EL1

VBAR_EL2 RW

UNK

64

B2.101 Vector Base Address Register, EL2

VBAR_EL3 RW

UNK

64

B2.102 Vector Base Address Register, EL3

B2 AArch64 system registers

B2.3 AArch64 Exception handling registers

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

B2-365

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......