B2.18

AArch64 Implementation defined registers

IMPLEMENTATION DEFINED

registers provide test features and any required configuration options specific to

the Cortex

‑

A35 processor.

The following table shows the

IMPLEMENTATION DEFINED

registers in AArch64 state. If a register is not

indicated as mapped to an AArch32 64-bit register, bits[63:32] are

0x00000000

.

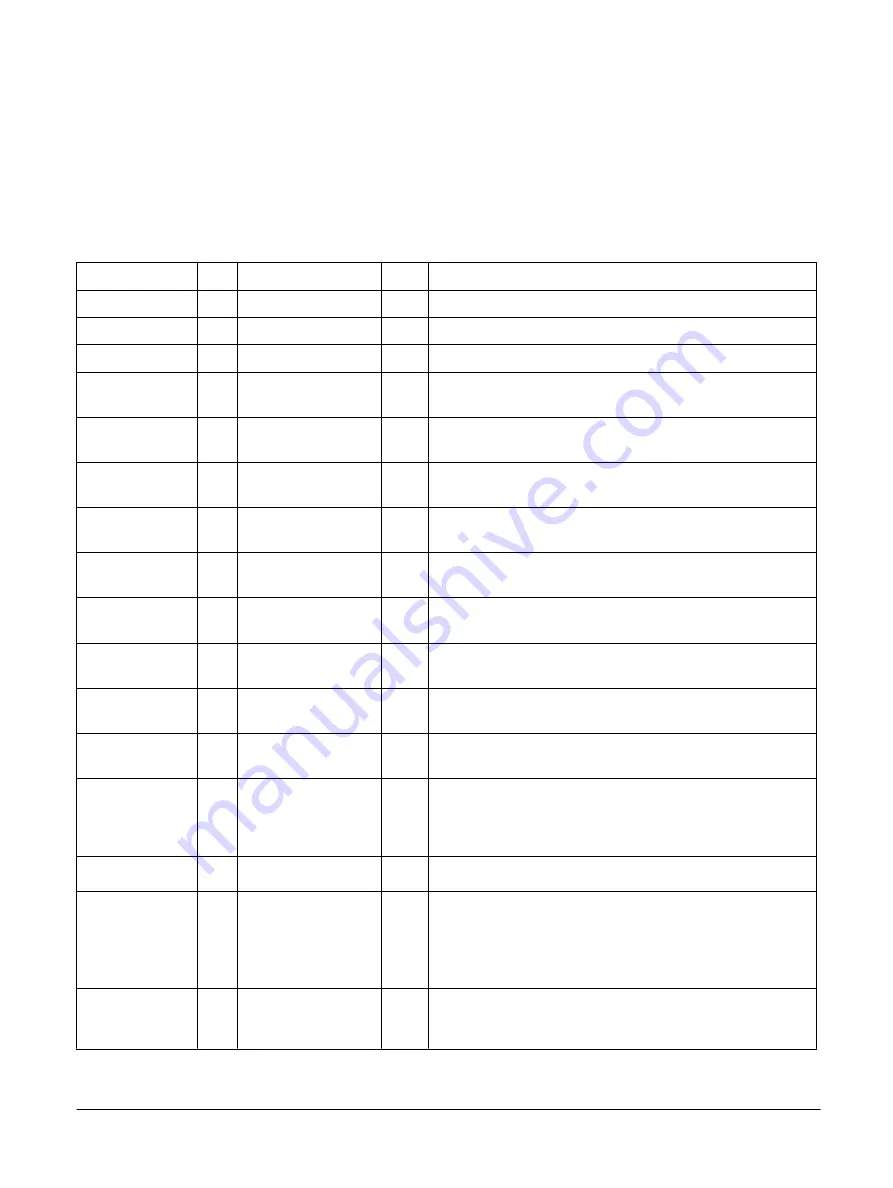

Table B2-17 AArch64 implementation defined registers

Name

Type Reset

Width Description

ACTLR_EL1

RW

0x00000000

32

B2.19 Auxiliary Control Register, EL1

ACTLR_EL2

RW

0x00000000

32

B2.20 Auxiliary Control Register, EL2

ACTLR_EL3

RW

0x00000000

32

B2.21 Auxiliary Control Register, EL3

AFSR0_EL1

RW

0x00000000

32

B2.22 Auxiliary Fault Status Register 0, EL1, EL2, and EL3

AFSR1_EL1

RW

0x00000000

32

B2.23 Auxiliary Fault Status Register 1, EL1, EL2, and EL3

AFSR0_EL2

RW

0x00000000

32

B2.22 Auxiliary Fault Status Register 0, EL1, EL2, and EL3

AFSR1_EL2

RW

0x00000000

32

B2.23 Auxiliary Fault Status Register 1, EL1, EL2, and EL3

AFSR0_EL3

RW

0x00000000

32

B2.22 Auxiliary Fault Status Register 0, EL1, EL2, and EL3

AFSR1_EL3

RW

0x00000000

32

B2.23 Auxiliary Fault Status Register 1, EL1, EL2, and EL3

AMAIR_EL1

RW

0x0000000000000000

64

B2.25 Auxiliary Memory Attribute Indirection Register, EL1

AMAIR_EL2

RW

0x0000000000000000

64

B2.26 Auxiliary Memory Attribute Indirection Register, EL2

AMAIR_EL3

RW

0x0000000000000000

64

B2.27 Auxiliary Memory Attribute Indirection Register, EL3

L2CTLR_EL1

RW

-

32

B2.74 L2 Control Register, EL1

The reset value depends on the processor implementation and the

state of the

L2RSTDISABLE

signal.

L2ECTLR_EL1

RW

0x00000000

32

B2.75 L2 Extended Control Register, EL1

L2ACTLR_EL1

RW

0x80000000

32

B2.73 L2 Auxiliary Control Register, EL1

This is the reset value for an ACE interface. For an AXI interface the

reset value is

0x 80000008

. For a CHI interface the reset value is

0x80004008

.

CPUACTLR_EL1

RW

0x00000000090CA000

64

B2.36 CPU Auxiliary Control Register, EL1

Mapped to a 64-bit AArch32 register.

B2 AArch64 system registers

B2.18 AArch64 Implementation defined registers

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

B2-384

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......