B2.37

CPU Extended Control Register, EL1

The CPUECTLR_EL1 characteristics are:

Purpose

Provides additional

IMPLEMENTATION DEFINED

configuration and control options for the processor.

Usage constraints

This register is accessible as follows:

EL0 EL1

(NS)

EL1

(S)

EL2 EL3

(SCR.NS = 1)

EL3

(SCR.NS = 0)

-

RW

RW RW RW

RW

The CPUECTLR_EL1 can be written dynamically.

The CPUECTLR_EL1 is write accessible in EL1 if ACTLR_EL3.CPUECTLR is 1 and

ACTLR_EL2.CPUECTLR is 1, or ACTLR_EL3.CPUECTLR is 1 and SCR.NS is 0.

The CPUECTLR_EL1 is write accessible in EL2 if ACTLR_EL3.CPUECTLR is 1.

Configurations

The CPUECTLR_EL1 is mapped to the AArch32 CPUECTLR register. See

.

Attributes

CPUECTLR_EL1 is a 64-bit register.

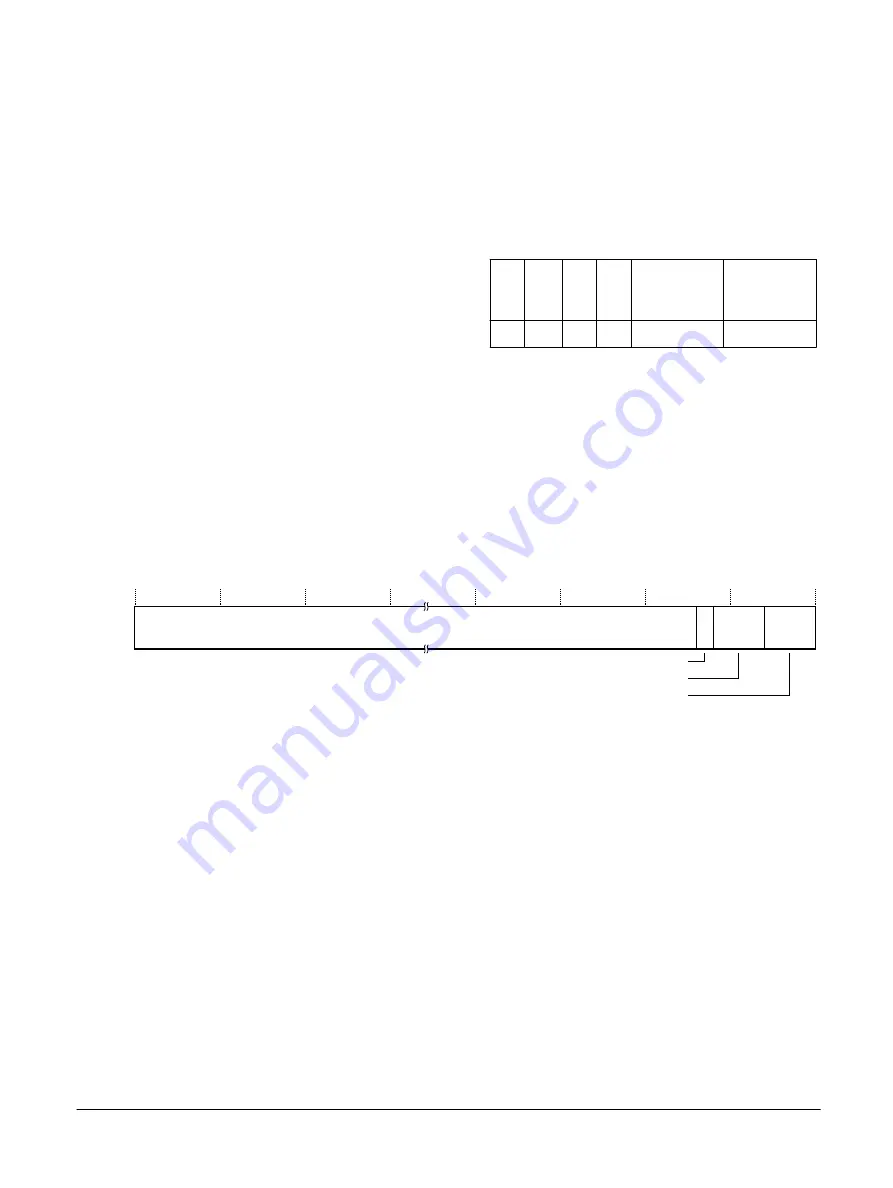

7 6 5

3 2

RES

0

0

63

SMPEN

FPRETCTL

CPURETCTL

Figure B2-12 CPUECTLR_EL1 bit assignments

[63:7]

Reserved,

RES0

.

SMPEN, [6]

Enable hardware management of data coherency with other cores in the cluster. The possible

values are:

0

Disables data coherency with other cores in the cluster. This is the reset value.

1

Enables data coherency with other cores in the cluster.

Set the SMPEN bit before enabling the caches, even if there is only one core in the system.

[5:3]

Advanced SIMD and floating-point retention control. The possible values are:

0b000

Disable the retention circuit. This is the reset value.

0b001

2 Architectural Timer ticks are required before retention entry.

0b010

8 Architectural Timer ticks are required before retention entry.

0b011

32 Architectural Timer ticks are required before retention entry.

B2 AArch64 system registers

B2.37 CPU Extended Control Register, EL1

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

B2-416

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......