B2.40

Data Cache Zero ID Register, EL0

The DCZID_EL0 characteristics are:

Purpose

Indicates the block size written with byte values of zero by the

DC ZVA

(Cache Zero by

Address), system instruction.

Usage constraints

This register is accessible as follows:

EL0 EL1

(NS)

EL1

(S)

EL2 EL3

(SCR.NS = 1)

EL3

(SCR.NS = 0)

RO

RO

RO

RO

RO

RO

Configurations

There are no configuration notes.

Attributes

DCZID_EL0 is a 32-bit register.

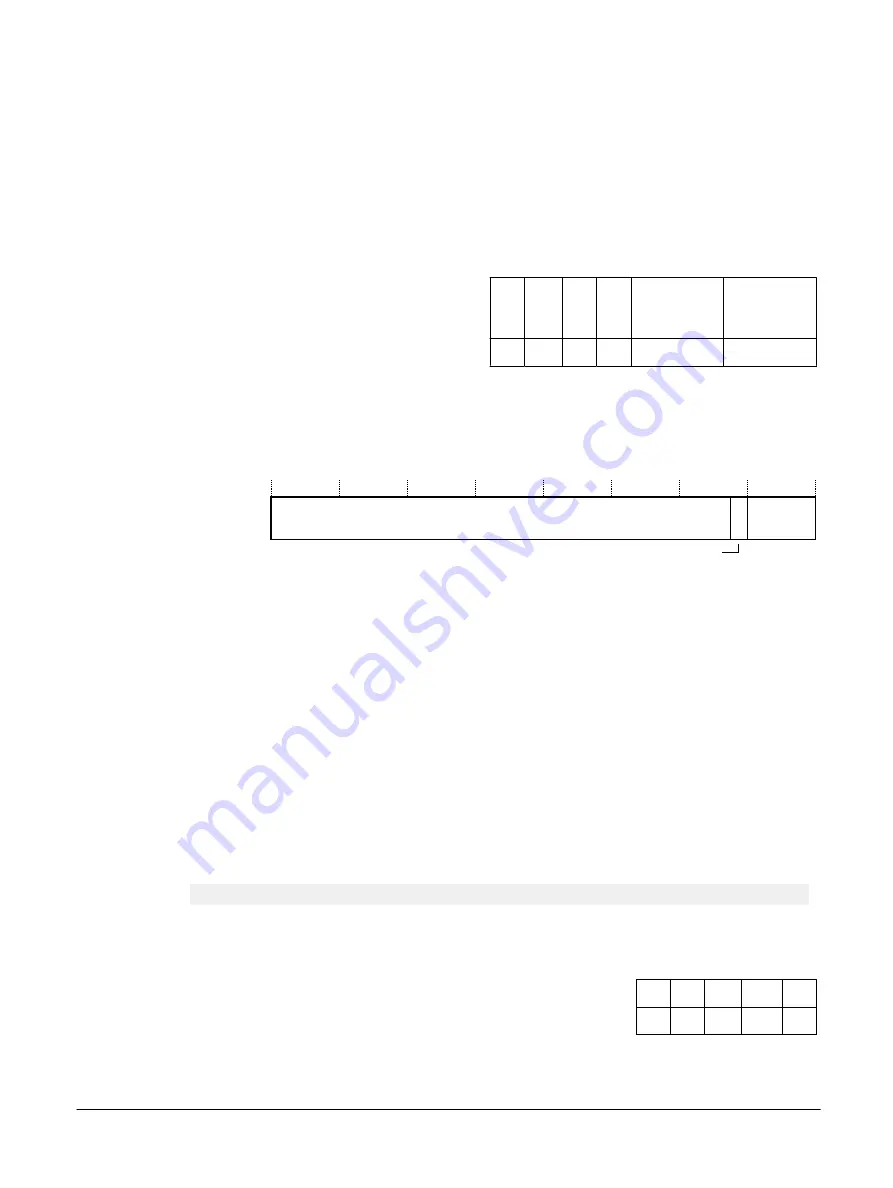

31

5 4 3

0

BlockSize

RES

0

DZP

Figure B2-15 DCZID_EL0 bit assignments

[32:5]

Reserved,

RES0

.

DZP, [4]

Prohibit the

DC ZVA

instruction:

0

DC ZVA

instruction permitted.

1

DC ZVA

instruction is prohibited.

BlockSize, [3:0]

Log2 of the block size in words:

0b0100

The block size is 16 words.

To access the DCZID_EL0:

MRS <Xt>, DCZID_EL0 ; Read DCZID_EL0 into Xt

Register access is encoded as follows:

Table B2-31 DCZID_EL0 access encoding

op0 op1 CRn CRm op2

11

011 0000 0000 111

B2 AArch64 system registers

B2.40 Data Cache Zero ID Register, EL0

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

B2-422

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......