B2.43

Exception Syndrome Register, EL3

The ESR_EL3 characteristics are:

Purpose

Holds syndrome information for an exception taken to EL3.

Usage constraints

This register is accessible as follows:

EL0 EL1

(NS)

EL1

(S)

EL2 EL3

(SCR.NS = 1)

EL3

(SCR.NS = 0)

-

-

-

-

RW

RW

Configurations

ESR_EL3 is mapped to AArch32 register DFSR(S). See

B1.49 Data Fault Status Register

.

Attributes

ESR_EL3 is a 32-bit register.

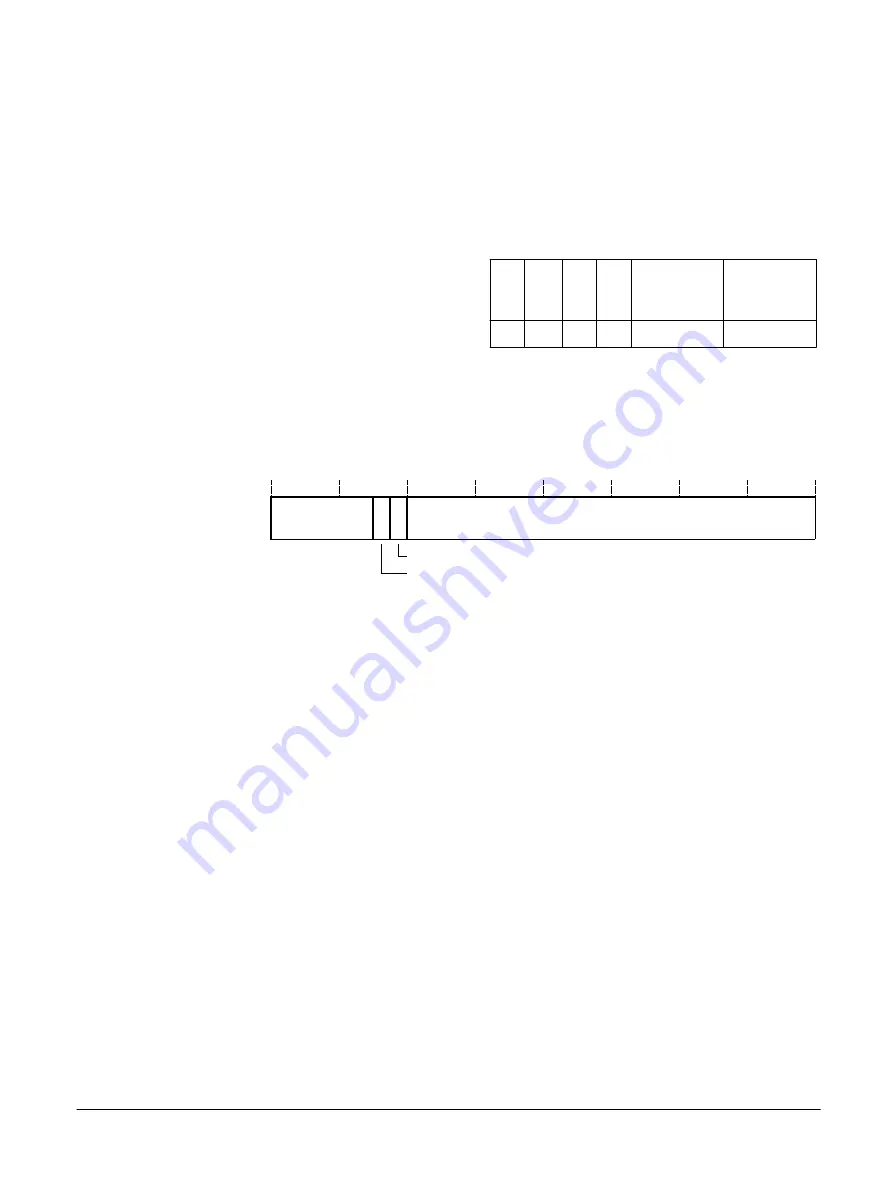

31

0

ISS

IL

EC

25 24

26

ISS Valid

23

Figure B2-18 ESR_EL3 bit assignments

EC, [31:26]

Exception Class. Indicates the reason for the exception that this register holds information

about.

IL, [25]

Instruction Length for synchronous exceptions. The possible values are:

0

16-bit.

1

32-bit.

This field is 1 for the SError interrupt, instruction aborts, misaligned PC, Stack pointer

misalignment, data aborts for which the ISV bit is 0, exceptions caused by an illegal instruction

set state, and exceptions using the

0x0

Exception Class.

ISS Valid, [24]

Syndrome valid. The possible values are:

0

ISS not valid, ISS is

RES0

.

1

ISS valid.

ISS, [23:0]

Syndrome information.

When the EC field is

0x2F

, indicating an SError interrupt has occurred, the ISS field contents are

IMPLEMENTATION DEFINED

.

B2 AArch64 system registers

B2.43 Exception Syndrome Register, EL3

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

B2-427

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......