B2.72

Interrupt Status Register, EL1

The ISR_EL1 characteristics are:

Purpose

Shows whether an IRQ, FIQ, or external abort is pending. An indicated pending abort might be

a physical abort or a virtual abort.

Usage constraints

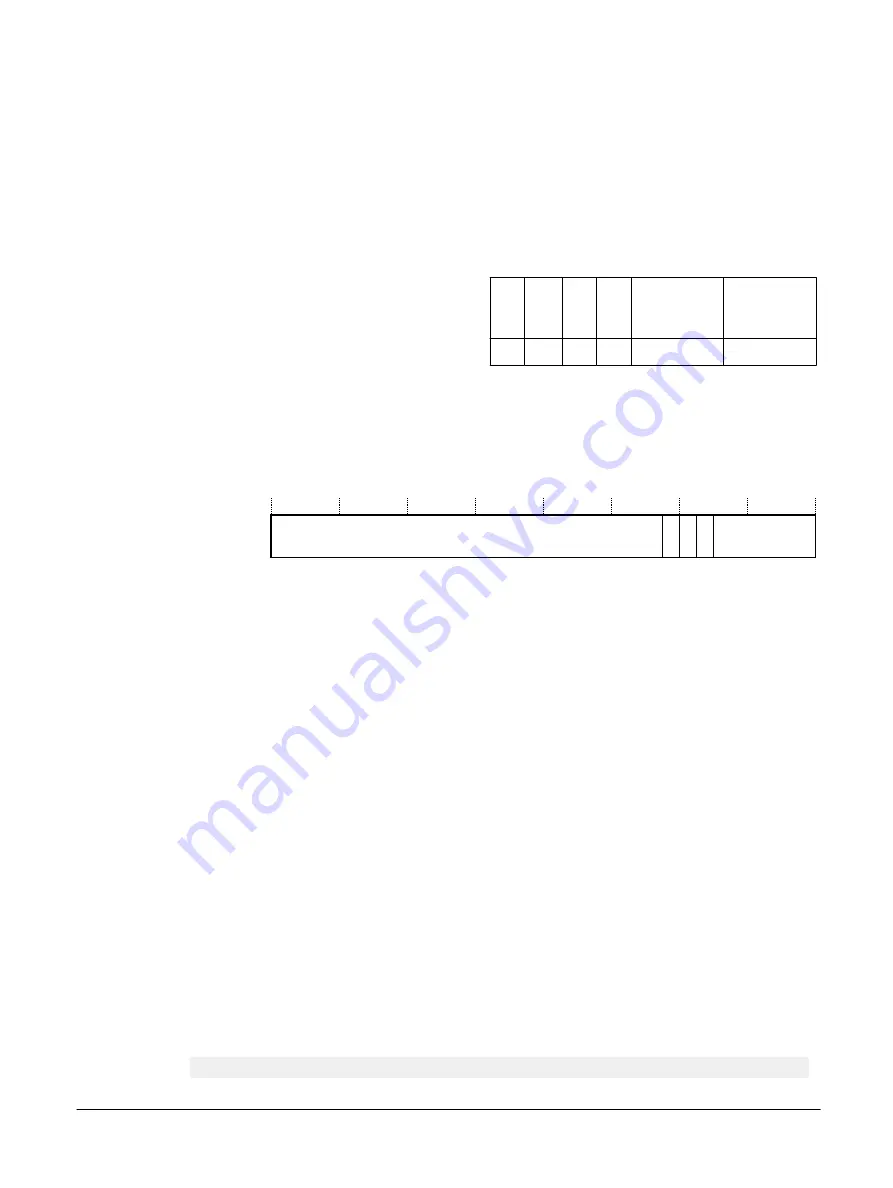

This register is accessible as follows:

EL0 EL1

(NS)

EL1

(S)

EL2 EL3

(SCR.NS = 1)

EL3

(SCR.NS = 0)

-

RO

RO

RO

RO

RO

Configurations

ISR_EL1 is architecturally mapped to AArch32 register ISR. See

Attributes

ISR_EL1 is a 32-bit register.

31

9 8 7 6 5

0

Reserved

F

I

A

Reserved

Figure B2-44 ISR_EL1 bit assignments

[31:9]

Reserved,

RES0

.

A, [8]

External abort pending bit:

0

No pending external abort.

1

An external abort is pending.

I, [7]

IRQ pending bit. Indicates whether an IRQ interrupt is pending:

0

No pending IRQ.

1

An IRQ interrupt is pending.

F, [6]

FIQ pending bit. Indicates whether an FIQ interrupt is pending:

0

No pending FIQ.

1

An FIQ interrupt is pending.

[5:0]

Reserved,

RES0

.

To access the ISR_EL1:

MRS <Xt>, ISR_EL1 ; Read ISR_EL1 into Xt

B2 AArch64 system registers

B2.72 Interrupt Status Register, EL1

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

B2-484

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......