B2.76

L2 Memory Error Syndrome Register, EL1

The L2MERRSR_EL1 characteristics are:

Purpose

Holds information about ECC errors on the:

• L2 data RAMs.

• L2 tag RAMs.

• SCU snoop filter RAMs.

Usage constraints

This register is accessible as follows:

EL0 EL1

(NS)

EL1

(S)

EL2 EL3

(SCR.NS = 1)

EL3

(SCR.NS = 0)

-

RW

RW RW RW

RW

Configurations

The L2MERRSR_EL1 is mapped to the AArch32 L2MERRSR register. See

.

There is one copy of this register that is used in both Secure and Non-secure states.

A write of any value to the register updates the register to

0x0000000000000000

.

Attributes

L2MERRSR_EL1 is a 64-bit register.

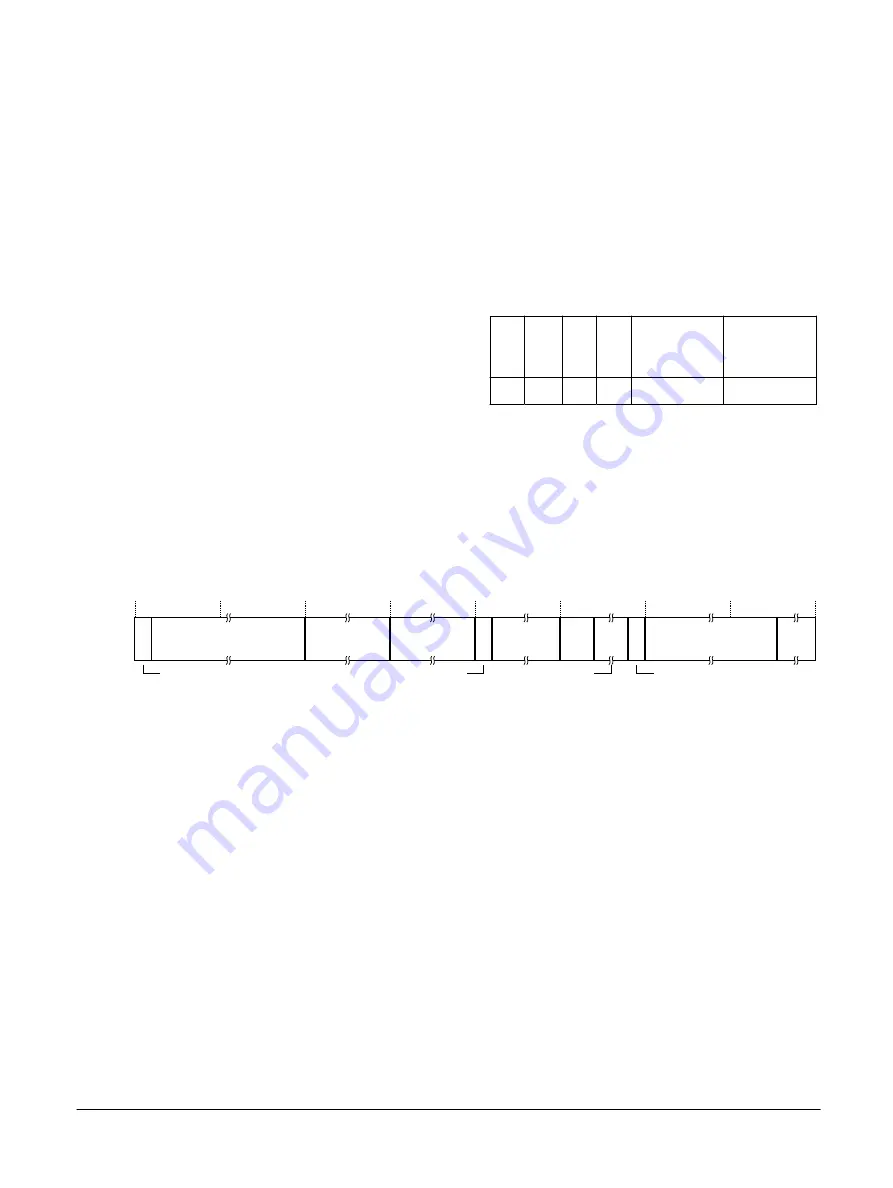

Fatal

24 23 22 21

Other error

count

Repeat error

count

31

32

0

63

RES

0

47

48

40 39

30

Valid

RAMID

18 17

CPUID/Way

RAM address

2

3

62

RES

0

RES

0

16

RES

0

Figure B2-48 L2MERRSR_EL1 bit assignments

Fatal, [63]

Fatal bit. This bit is set to 1 on the first memory error that caused a data abort. It is a sticky bit

so that after it is set, it remains set until the register is written.

The reset value is 0.

[62:48]

Reserved,

RES0

.

Other error count, [47:40]

This field is set to 0 on the first memory error and is incremented on any memory error that does

not match the RAMID and Bank/Way information in this register while the sticky Valid bit is

set.

The reset value is 0.

Repeat error count, [39:32]

This field is set to 0 on the first memory error and is incremented on any memory error that

exactly matches the RAMID and Bank/Way information in this register while the sticky Valid

bit is set.

The reset value is 0.

B2 AArch64 system registers

B2.76 L2 Memory Error Syndrome Register, EL1

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

B2-493

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......