B2.85

Physical Address Register, EL1

The PAR_EL1 characteristics are:

Purpose

The Physical Address returned from an address translation.

Usage constraints

This register is accessible as follows:

EL0 EL1

(NS)

EL1

(S)

EL2 EL3

(SCR.NS = 1)

EL3

(SCR.NS = 0)

-

RW

RW RW RW

RW

Configurations

PAR_EL1 is architecturally mapped to AArch32 register PAR(NS). See

.

Attributes

PAR_EL1 is a 64-bit register.

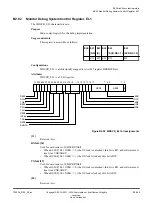

The following figure shows the PAR_EL1 bit assignments when the Virtual Address to Physical Address

conversion completes successfully.

RES

0

F

56 55

48 47

59

60

7 6

SHA

10 9 8

12 11

RES

1

NS

AttrL

RES

0

PA

0

63

AttrH

RES

0

Figure B2-55 PAR_EL1 pass bit assignments

The following list shows the PAR_EL1 bit assignments when the Virtual Address to Physical Address

conversion completes successfully.

AttrH, [63:60]

Defines Normal or Device memory and outer cacheability. Must be used in conjunction with

AttrL. The possible values are:

0b0000

Device memory, see Attr[3:0].

0b0100

Normal memory, Outer Non-cacheable.

0b1000

Normal memory, Outer Write-Through Cacheable.

0b1001

Normal memory, Outer Write-Through Cacheable, Outer Write-Allocate.

0b1010

Normal memory, Outer Write-Through Cacheable, Outer Read-Allocate.

0b1011

Normal memory, Outer Write-Through Cacheable, Outer WriteAllocate, Outer Read-

Allocate.

0b1100

Normal memory, Outer Write-Back Cacheable.

0b1101

Normal memory, Outer Write-Back Cacheable, Outer Write-Allocate.

0b1110

Normal memory, Outer Write-Back Cacheable, Outer Read-Allocate.

0b1111

Normal memory, Outer Write-Back Cacheable, Outer Write-Allocate, Outer Read-

Allocate.

All other values are reserved.

AttrL, [59:56]

B2 AArch64 system registers

B2.85 Physical Address Register, EL1

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

B2-514

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......