B3.2

Active Priority Register

The GICC_APR0 characteristics are:

Purpose

Provides support for preserving and restoring state in power management applications.

Usage constraints

This register is banked to provide Secure and Non-secure copies. This ensures that Non-secure

accesses do not interfere with Secure operation.

Configurations

Available in all configurations.

Attributes

See the register summary in

B3.1 CPU interface register summary

.

The Cortex

‑

A35 processor implements the GICC_APR0 according to the recommendations described in

the

Arm Generic Interrupt Controller Architecture Specification

.

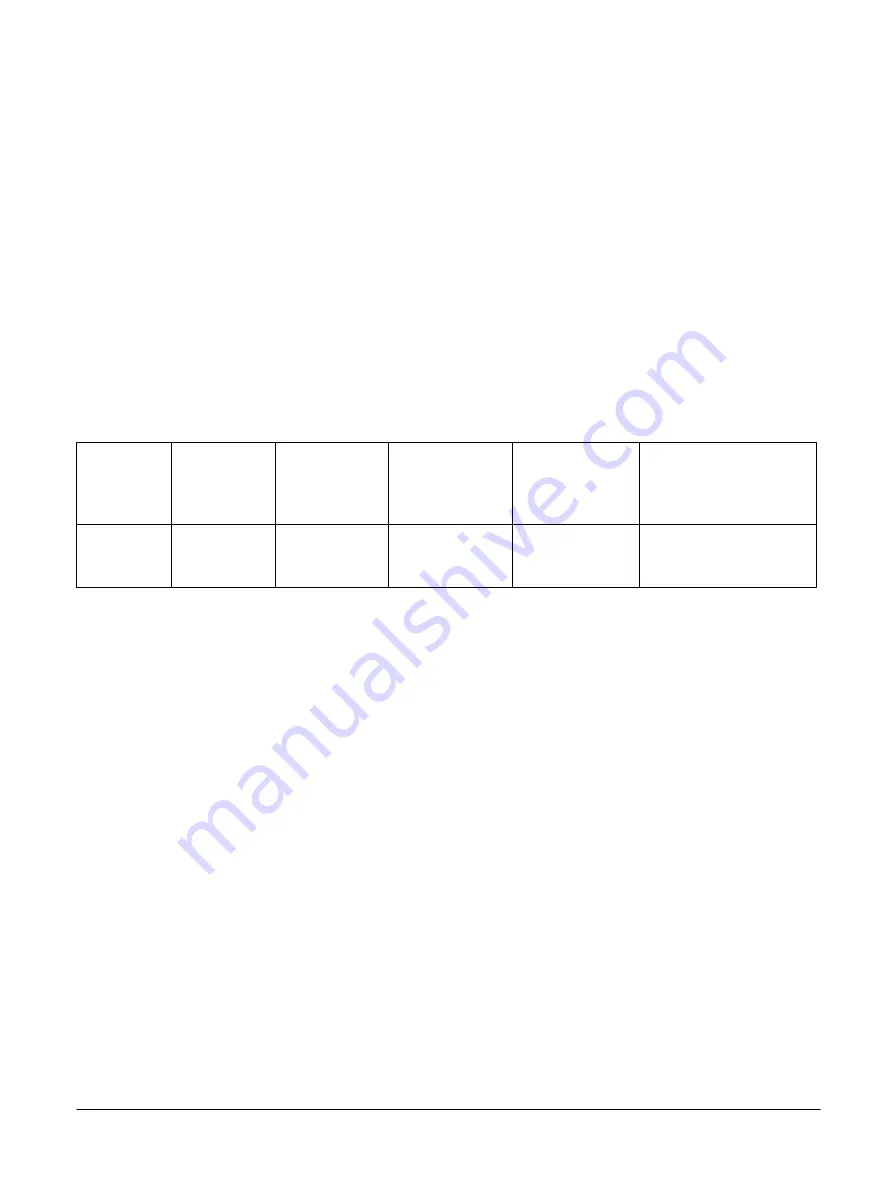

Table B3-2 Active Priority Register implementation

Number of

group

priority bits

Preemption

levels

Minimum value

of Secure

GICC_BPR

Minimum legal

value of Non-

secure

GICC_BPR

Active Priority

Registers

implemented

View of Active Priority

Registers for Non-secure

accesses

5

32

2

3

GICC_APR0 [31:0]

GICC_NSAPR0 [31:16]

appears as GICC_APRo

[15:0]

B3 GIC registers

B3.2 Active Priority Register

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

B3-561

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......